# Accelerator Benchmark Suite Using OpenACC Directives

A Thesis Presented to the Faculty of the Department of Computer Science

University of Houston

In Partial Fulfillment of the Requirements for the Degree

Master of Science

Ву

Pooja Chitral

December 2014

# Accelerator Benchmark Suite Using OpenACC Directives

| Pooja Chitral                         |

|---------------------------------------|

| APPROVED:                             |

|                                       |

| Dr. Barbara Chapman, Chairman         |

| Dept. of Computer Science             |

|                                       |

| Dr. Omprakash Gnawali                 |

| Dept. of Computer Science             |

|                                       |

| Dr. Deniz Gurkan                      |

| Dept. of Technology                   |

|                                       |

| Dean, College of Natural Sciences and |

| Mathematics                           |

## Acknowledgements

I would like to express my gratitude to my advisor, Dr. Barbara Chapman, for giving me an excellent opportunity to be part of the HPC (High Performance Computing) Tools group. It was an absolute privilege to work under her tutelage as she inspired me to explore prospective research topics and provided her feedback during the course of my stay. It's my privilege to be part of such an enthusiastic, energetic, and inspiring team.

I would also like to extend my sincere gratitude to my mentor, Dr. Sunita Chandrashekaran. Her continuous guidance and support throughout my research work have been tremendous. Her directions at every point of my thesis helped me understand the problem better and motivated me to resolve them in the right spirit.

I would like to thank everyone in the HPC Tools group who has helped and motivated me at one point or another. I extend my gratitude to the Department of Computer Science for giving me this opportunity to be part of such a prestigious department at the University of Houston.

Last but not least, I would like to thank my family and friends who motivated and supported me throughout this journey. I would like to thank one of the most important persons in my life, my grandmother, for always inspiring me and believing in me.

# Accelerator Benchmark Suite Using OpenACC Directives

An Abstract of a Thesis

Presented to

the Faculty of the Department of Computer Science

University of Houston

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

By

Pooja Chitral

December 2014

## **Abstract**

In recent years, GPU computing has been very popular for scientific applications, especially after the release of programming languages like CUDA, OpenCL, and OpenACC. The growing popularity of GPU computation in commercial and scientific fields is attributed to the high computational power of GPU cores. The accelerator benchmark suite using OpenACC 2.0 is a combination of very popular benchmarks – the Parboil and NAS Parallel benchmarks. These benchmarks contain a wide range of throughput computing applications, which are useful for studying the performance of computing architectures and compilers. The Parboil benchmark includes applications from different scientific and commercial fields including image processing, biomolecular simulation, and astronomy. The NAS Parallel benchmark has a set of applications that target different areas of computational fluid dynamics.

The accelerator benchmark suite that has been designed exploits the computational power of GPU architecture by using the emerging directives and clauses provided by OpenACC 2.0. This benchmark can act as a reference point for new programmers in GPU computing, reducing the time taken to understand one of the most powerful parallel programming paradigms.

Finally, the goal of the accelerator benchmark is to evaluate the applicability of one of the high-level programming models OpenACC for accelerators. This benchmark will help provide the OpenACC community with valuable feedback to improve the model further.

# **Table of Contents**

| Chapter 1. Introduction                                  | 1  |

|----------------------------------------------------------|----|

| 1.1 Problem Statement                                    | 2  |

| 1.2 Thesis Contribution                                  | 3  |

| 1.3 Thesis Outline                                       | 5  |

| Chapter 2. Emerging Heterogeneous Systems                | 6  |

| 2.1 Need for Heterogeneous Computing                     | 6  |

| 2.2 Heterogeneous Systems                                | 7  |

| 2.2.1 Graphical Processing Unit (GPU)                    | 7  |

| 2.2.2 Digital Signal Processor (DSP)                     | 9  |

| 2.3 Challenges in Heterogeneous Computing                | 11 |

| 2.3.1 Programming Model Support                          | 11 |

| 2.3.2 Data Transfer                                      | 12 |

| 2.3.3 Memory Management                                  | 12 |

| Chapter 3. GPUs for Extreme Computing – State-of-the-Art | 14 |

| 3.1 Evolution of GPUs                                    | 14 |

| 3.2 NVIDIA GPUs                                          | 19 |

| 3.2.1 NVIDIA GPU Acceleration                            | 19 |

| 3.2.2 Kepler Architecture                                | 21 |

| 3.3 AMD APUs                                             | 26 |

| 3.3.1 Heterogeneous System Architecture                  | 27 |

| 3.3.2 Kaveri Architecture                               | 30 |

|---------------------------------------------------------|----|

| Chapter 4. Programming Models for Heterogeneous Systems | 34 |

| 4.1 CUDA                                                | 34 |

| 4.2 OpenACC                                             | 40 |

| 4.3 OpenMP                                              | 43 |

| 4.3.1 Memory Model of OpenMP                            | 44 |

| 4.3.2 Execution Model of OpenMP                         | 45 |

| 4.3.3 OpenMP Programming Directives                     | 45 |

| 4.4 OpenCL                                              | 51 |

| Chapter 5. Developing an Accelerator Benchmark Suite    | 52 |

| 5.1 Heterogeneous Benchmark Suite                       | 53 |

| 5.1.1 Overview                                          | 53 |

| 5.2 Using OpenACC 2.0                                   | 56 |

| 5.2.1 Routine Directive                                 | 56 |

| 5.2.2 Nested OpenACC Regions                            | 57 |

| 5.2.3 Unstructured Data Regions                         | 58 |

| 5.2.4 Atomic Directive                                  | 60 |

| 5.2.5 Tile Construct                                    | 61 |

| 5.2.6 Support for Multiple Device Types                 | 62 |

| 5.2.7 Extended Runtime API                              | 63 |

| 5.3 Testbed Setup                                       | 64 |

| 5 4 Parhoil OpenACC 2 0                                 | 65 |

| 5.4.1 Benchmark Porting and Result Analysis      | 66  |

|--------------------------------------------------|-----|

| 5.5 NAS Parallel Benchmark                       | 88  |

| 5.6 Analysis and Observations                    | 100 |

| Chapter 6. Conclusion and Future Work            | 103 |

| 6.1 Conclusion                                   | 103 |

| 6.2 Future Work                                  | 105 |

| Bibliography                                     | 106 |

| Appendix A                                       | 110 |

| Compiling and Running Benchmarks                 | 110 |

| A1. Compiling and Running Parboil Benchmark      | 110 |

| A2. Compiling and Running NAS Parallel Benchmark | 111 |

| Appendix B                                       | 114 |

| Explanation of Abbreviations                     | 114 |

# **List of Figures**

| Figure 3.1: Trends in GPU Computing [15]                               |

|------------------------------------------------------------------------|

| Figure 3.2: Comparing CPU and GPU Compute Cores [18]                   |

| Figure 3.3: How GPU Acceleration Works [18]                            |

| Figure 3.4: Floating-point Operations per Second for CPU and GPU [30]  |

| Figure 3.5: Memory Bandwidth for CPU and GPU [30]                      |

| Figure 3.6: Three Ways to Accelerate Applications for NVIDIA GPUs [19] |

| Figure 3.7: Kepler GK110 Full Chip Block Diagram [24]                  |

| Figure 3.8: Streaming Multiprocessor (SMX) Architecture [24]           |

| Figure 3.9: Kepler Memory Hierarchy [24]                               |

| Figure 3.10: Heterogeneous System Architecture [26]                    |

| Figure 3.11: Kaveri APU [29]                                           |

| Figure 3.12: Block Diagram of Kaveri – hUMA [29]                       |

| Figure 3.13: Kaveri hQ [29]                                            |

| Figure 4.1: Grid of Thread Blocks [30]                                 |

| Figure 4.2: Memory Hierarchy [30]                                      |

| Figure 4.3: Memory Model for OpenMP [31]                               |

| Figure 4.4: Fork-join OpenMP Execution Model [48]                      |

| Figure 4.5: Work-sharing Constructs [31]                               |

| Figure 5.1: Architecture of the Coil System                            |

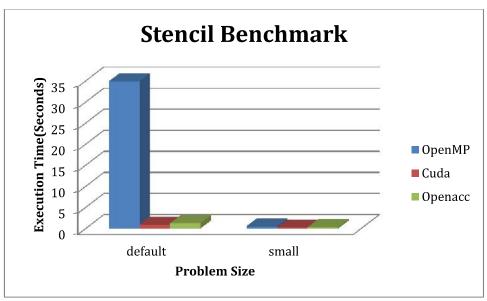

| Figure 5.2: Execution Time Graph – Stencil                             |

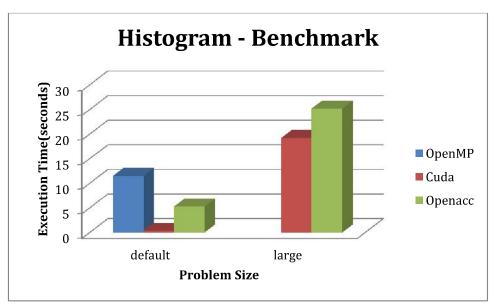

| Figure 5.3: Execution Time Graph - Histogram | 73 |

|----------------------------------------------|----|

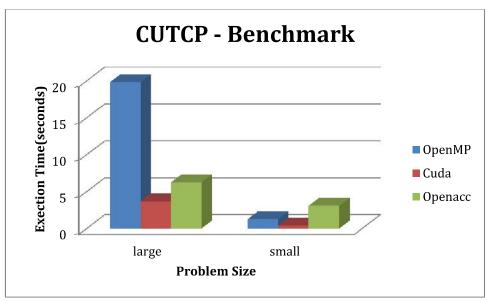

| Figure 5.4: Execution Time Graph – CUTCP     | 75 |

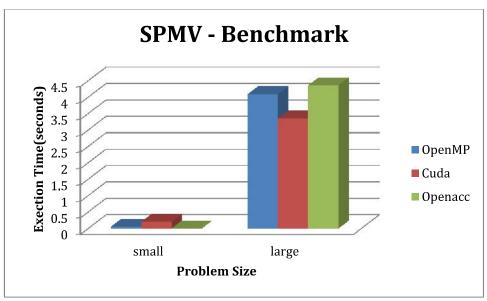

| Figure 5.5: Execution Time Graph – SPMV      | 77 |

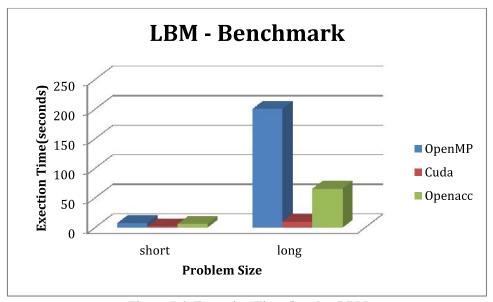

| Figure 5.6: Execution Time Graph – LBM       | 79 |

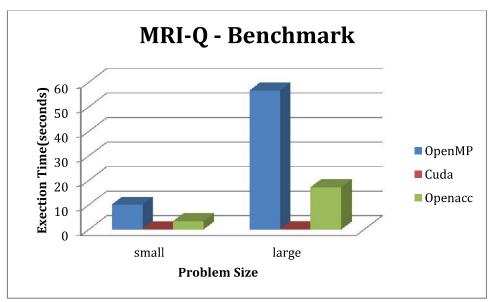

| Figure 5.7: Execution Time Graph – MRI-Q     | 82 |

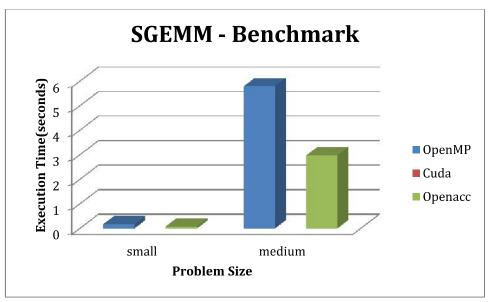

| Figure 5.8: Execution Time Graph - SGEMM     | 86 |

# **List of Tables**

| Table 4.1: Code Snippet for Matrix Multiplication using CUDA [30]          | 36 |

|----------------------------------------------------------------------------|----|

| Table 4.2: OpenACC Pragma's Syntax                                         | 41 |

| Table 4.3: Code Snippet for Sample Kernel Constructs                       | 42 |

| Table 4.4: Code Snippet for Sample Parallel Constructs                     | 43 |

| Table 4.5: OpenMP Directive Usage                                          | 46 |

| Table 4.6: Sample OpenMP Code Snippet                                      | 47 |

| Table 4.7: OpenMP Task Clauses                                             | 49 |

| Table 5.1: Usage of Routine Directive [35]                                 | 57 |

| Table 5.2: Nested Parallel Regions                                         | 58 |

| Table 5.3: Unstructured Data Lifetime [35]                                 | 59 |

| Table 5.4: Atomic Construct                                                | 61 |

| Table 5.5: Explaining Tile Clause Code Snippet                             | 61 |

| Table 5.6: Syntax for Using Multiple Device Types [43]                     | 62 |

| Table 5.7: New OpenACC 2.0 Clauses and Directives for Data Management [45] | 63 |

| Table 5.8: Stencil Code Snippet                                            | 68 |

| Table 5.9: Use of Atomic Update in Histogram                               | 71 |

| Table 5.10: Unstructured Data Lifetime Feature                             | 72 |

| Table 5.11: Code Snippet for CUTCP                                         | 74 |

| Table 5.12: Code Snippet for SPMV Compute Loop                                | 76    |

|-------------------------------------------------------------------------------|-------|

| Table 5.13: LBM Functions                                                     | 78    |

| Table 5.14: Code Snippet for ComputeQ CPU Function                            | 81    |

| Table 5.15: Code Snippet for Vectorising Column Major Matrixes to Vector Arra | ıy 83 |

| Table 5.16: Code Snippet for SGEMM – sgemm_kernel                             | 84    |

| Table 5.17: Code Snippet for BFS OpenMP Version                               | 87    |

| Table 5.18: Randlc_ep Function                                                | 91    |

| Table 5.19: EP Code Snippet                                                   | 93    |

| Table 5.20: FT Code Snippet for return_complex_abs Routine                    | 95    |

| Table 5.21: MG Inline Functions Replaced by Routine Functions                 | 97    |

| Table 5.22: Vranlc Function Snippet                                           | 98    |

| Table 5.23: Bubble Function in MG                                             | 99    |

| Table 5.24: Mons Comparison between OpenACC 1.0 and OpenACC 2.0               | 100   |

### **Chapter 1. Introduction**

Benchmarks are a set of programs designed for a very specific field, such as scientific computing, computational fluid dynamics, commercial applications, numerical analysis, and image processing. Many benchmarks are designed to target particular architectures. We use benchmarks for measuring performance characteristics related to the target platforms such as database management systems, I/O benchmarks, micro-benchmarks, parallel benchmarks, etc.

Benchmarks are extremely important in research, as they can be used to evaluate new technologies, architectures, and languages at their inception. Many vendors are willing to invest in the new technologies and research when the results of these benchmarks are promising. Benchmarks play a very important role in computer architecture research by helping programmers work on a set of shared data code and understand the behavior and performance of various technologies and system architecture. Benchmarks can also assist in understanding the best optimization techniques with respect to the computing architecture and the programming environment by enabling the comparison of different result sets.

#### 1.1 Problem Statement

The main aim of the created accelerator benchmark is to understand GPU computing in general, specifically OpenACC. This setup gives insight into OpenACC 1.0 features and how OpenACC 2.0 has improved drastically by implementing more advanced features. OpenACC 2.0 simplifies application portability, thereby improving the productivity of the developer.

OpenACC is an emerging accelerator model, and a lot of work has been done to improve features of OpenACC while maintaining performance improvement and portability aspects in mind.

Porting using OpenACC 1.0 is cumbersome, as it involves a lot of code restructuring, function inlining, etc. With OpenACC 2.0, porting of an application is easy and can be done in a more natural way that helps achieve the best performance for sequential code. OpenACC 2.0 drastically improves productivity and also adds flexibility in data handling by providing clauses for expressing an unstructured data lifetime for the variables.

#### 1.2 Thesis Contribution

- Developing an accelerator benchmark suite helped us study and analyze the

emerging high-level programming model OpenACC 2.0. The benchmark is used

to evaluate different types of computations to characterize execution behavior of

several of the most frequently used OpenACC features. We also present different

challenges while porting existing multithreaded accelerator benchmark suites to

GPUs.

- Applications from the Parboil benchmark were ported to GPUs using OpenACC 2.0. The unique challenges while porting programs from OpenMP and the serial version to OpenACC are analyzed and discussed. As Parboil implements applications from different domains, the accelerator benchmark suite can give an overview of how to port applications from different architecture to accelerator architecture.

- OpenACC is an evolving programming model. Although NAS Parallel Benchmark codes were ported to OpenACC 1.0 [46], there were several limitations posed by the version of OpenACC (V 1.0) used for that work. In this thesis, those limitations are overcome by using the most recent version of the specification, OpenACC 2.0, that fills some of the programming gaps discussed in

- [46]. Routine directives, unstructured data lifetime, and optimization techniques were some of the features used for this work.

- We analyzed the performance of OpenACC applications by comparing their performances with the alternative, accelerated version that used CUDA, OpenMP, and OpenCL. We optimized the accelerator benchmark suite applications by applying the loop collapse, loop unrolling, code restructuring, and some new data management techniques.

#### 1.3 Thesis Outline

This thesis is organized into the following sections:

Chapter 2 introduces heterogeneous computing, the need for heterogeneous computing, and popular heterogeneous systems used in scientific and commercial computing. It also describes different challenges in heterogeneous computing.

Chapter 3 discusses the evolution of GPUs, the architecture of NVIDIA and AMD GPUs, including latest Kepler GPU from NVIDIA and Kaveri from AMD.

Chapter 4 presents some of the popular programming models for accelerators like CUDA, OpenMP, OpenACC, and OpenCL.

Chapter 5 provides the rationale for creating the accelerator benchmark suite. This chapter also involves discussion of OpenACC 2.0 features and how they are used in the accelerator benchmark. Further, we discuss implementation details of OpenACC 2.0 for NPB and Parboil benchmarks and performance analysis for the same.

Chapter 6 presents conclusions and related future work.

## **Chapter 2. Emerging Heterogeneous Systems**

The heterogeneous computing environment, in contrast to the homogeneous systems, is a combination of different processing units. For some applications, we see considerable performance improvement when we combine different processing elements that incorporate special processing capabilities while handling some aspects of tasks, instead of adding more homogeneous cores [3].

A heterogeneous computing environment presents new challenges, as different architectures have different memory and execution models. The level of heterogeneity in the system can introduce non-uniformity in system development, programming practices, and overall system capability [1].

#### 2.1 Need for Heterogeneous Computing

Understanding the nature of the application in terms of structure of the program, computational needs, and memory requirements will help us decide which devices will deliver better performance and productivity. Unlike CPUs, which are designed for handling large sequential programs with significant branching and complexity, GPUs are good for performing computationally intense applications with considerably less branching and complexity.

HPC allows exploitation of the inherent capabilities of a wide range of accelerators to solve computationally intensive problems.

The importance of heterogeneous computing is that we can achieve very large performance gains if we can consolidate and integrate the strengths of all the different platforms used. GPUs is excellent for floating point operations [4]. Multicore CPUs are good for command and control operations. FPGAs is an ideal solution for all kinds of operations other than floating point operations like binary, integer, fix point, text, and special formats [5]. As quoted by different companies that comprise the high-performance computing industry, "The future is heterogeneous" [54].

When we study the problems prevalent in heterogeneous systems, we divide the entire problem into many subproblems and then categorize and distribute these problems to different processing elements designed for specific types of operations.

#### 2.2 Heterogeneous Systems

Coprocessors are used to supplement the functions of the primary processor or CPU. These are attached to the CPU via interconnect. Computationally intensive tasks can be offloaded to coprocessors in order to accelerate the performance of the application (coprocessors can be anything from general-purpose CPUs, GPUs, FPGAs, etc.).

#### 2.2.1 Graphical Processing Unit (GPU)

The Graphical Processing Unit (GPU) is a specialized electronic circuit created to perform graphical processing operations. Computer graphics is fundamentally an

"embarrassingly" parallel-problem as the workload can easily be spread across multiple compute unit, since each pixel on the screen can (mostly) be worked on independently [6].

GPUs are very fast compared to CPUs because every GPU contains hundreds of thousands "GPU cores" internally. And these cores work in parallel, as they are independent of each other while performing the computation. Thus, for some applications, using GPU cores is much better than adding more CPU cores.

As mentioned earlier, GPUs are specifically designed for graphics processing. Thus, they have very restricted operations, and their programming model is not same as CPU computing. To maximize GPU performance, programs are executed using streaming processing model [54].

A "stream" can simply be a set of data that requires similar computation, by providing data parallelism. As each data set is computed independently, there is no scope for having static or shared data in streaming processing. The order of the workflow would be to read the input, compute the results using input data, and then write the output back to the host device [54].

Ideally, GPU applications should have large data sets with structured loops for high parallelism and minimal dependency between data elements.

In our early efforts for harnessing the power of GPUs for general purpose computing, we used OpenGL and DirectX API. These APIs were difficult to understand and reduced productivity of the programmers. Later in 2006, NVIDIA developed a

CUDA programming extension for C/C++ and FORTRAN. OpenACC is a programming standard for parallel computing developed by Cray, CAPS, NVIDIA, and PGI.

#### 2.2.2 Digital Signal Processor (DSP)

A digital signal processor (DSP) is a microprocessor chip that is widely used in many electronic devices. DSPs take signals as input, digitizes them by enhancing the quality, and then apply mathematical functions and manipulates them for the target application.

Though general-purpose DSPs can be used for many of the manipulations, it is very practical to have a dedicated DSP for specific applications. Portability is one of the major advantages of dedicated DSPs, as they address the power constraints associated with devices like mobile phones [7].

DSPs process the data in real time with precise output. Thus DSPs are used in audio signal processing, audio and video compression, speech processing and recognition, digital image processing, digital communications, biomedicine, seismology, and radar applications [7].

Digital signal processing typically requires a large number of mathematical operations to be performed concurrently on a large set of data. Heavy computation in the DSP is due to continuous conversion of data from analog to digital and vice versa [7].

One of the very important bottlenecks in digital signal processing is the transfer of data to and from memory. Memory-transfer operations typically include data from the signals to be processed, the instructions for processing the data, and the binary code that

needs to be fed to the sequencer. Because of the high intensity of data processing and data movement in the memory DSPs have a special architecture [7].

#### 2.2.2.1 Keystone Architecture

Keystone architecture is based on Texas Instruments (TI)'s System-on-Chip (SoC) processors. The design methodology and the architecture enable high-performance gains. This architecture gives the flexibility to include a single or multicore mix of DSP [8] [9]. Keystone architecture has a C66x Core Pac, memory subsystem, application-specific coprocessor, multicore navigator, network coprocessor, interfaces, embedded trace buffer, and system trace buffers for debugging. Keystone architecture can be used in many of the important wireless applications like base-station transceiver systems, cellular systems like 3G, 4G. Some of the media applications using keystone architecture are video infrastructure, medical imaging, military and defense, smart grids, etc. Because of the SoC concept, C66x-generation DSPs maximize throughput of on-chip data flows by eliminating the most important bottleneck caused by data flow. One of the very important features of this architecture is TeraNet, which is a packet-based high-speed non-blocking channel that transfers as much as two terabytes of data per second [8] [10].

With TeraNet and an extensive two-layer memory structure, data flows freely and effectively through C66x devices. Although it provides direct chip-to-chip connectivity for local devices, hyperlink is also integral to the internal processing architecture of C66x DSPs. The hyperlink is a fast and efficient interface with low protocol overhead and high throughput, running at an aggregate speed of 50 Gbps (four lanes at 12.5 Gbps each).

Working in conjunction with Multicore Navigator, Hyperlink transparently dispatches tasks to other local devices where they are executed as if they were being processed on local resources. In the keystone architecture, CorePac is defined as the main processing element in a multicore SoC. CorePac includes the infrastructure that supports the DSP cores, including shared memory and memory controllers. There are three levels of memory in the keystone architecture. Each C66x CorePac has level-1 program (L1P) and level-1 data (L1D) memory [8] [10].

#### 2.3 Challenges in Heterogeneous Computing

Computing in a heterogeneous environment requires the separate compilation of code for different architectures. Mapping of the sub-programs on different architectures can sometimes be challenging. In a heterogeneous environment, program debugging becomes increasingly complicated because of heterogeneity [12].

#### 2.3.1 Programming Model Support

When programming in a heterogeneous environment, it is very important to have an efficient programming model that will help us maximize computational output from the underlying architecture. The programming model should be easy to understand and follow a natural migration path from serial programs, without affecting the productivity of the programmer. These programming models should also allow portability across multiple machine generations. Finally, the programming model should provide evolved

API's that will hide the low-level details of the underlying hardware, thus making heterogeneous programming seamless.

#### 2.3.2 Data Transfer

In heterogeneous computing, the host is connected to all its devices via an interconnect. Thus, it is very important to understand the data transfer rate and limitations of interconnects to optimize the data transfers between hosts and devices. This will help in understanding how and when the data should be moved to the device and returned to the host. Neglecting data activity will undermine the entire computation and, in turn, lead to a performance reduction caused by bottlenecks in the interconnect.

Heterogeneous systems typically have hundreds and thousands of computing nodes when compared to many-core processors with more than 100 cores on a single electronic chip. This increases the distance between the memory and cores, placing limitations on the electronic networks used to connect the systems. The latency for accessing the external memory modules differs strongly, depending on the distance between the cores and memory and its locality in the network [11].

#### 2.3.3 Memory Management

In multicore computing, parallelism is spread across multiple system levels, and the data used for computation is stored redundantly in memory subsystems at several levels. From 1986 to 2000, CPU speed improved at an annual rate of 55%, while memory speed only

improved by 10% [13]. As cores become faster and faster, data moves in and out, leading to a bottleneck in the supply of data for computations.

As heterogeneous computing is host-directed, CPU allocates tasks to the connected subsystems. Thus, the entire computation moves to the device space, and then the results are brought back to the host.

As different systems have a different memory hierarchy and their private memory for computation, it is very important to synchronize these two memories between the host and device and also schedule tasks as effectively as possible.

The devices mainly differ in the configuration and arrangement of functional and control units, and the data flow from the main memory to the compute cores is organized differently. Consequently, the instruction set and the generic or vendor-specific programming concepts differ. In some programming approaches, only parts of the hardware structure are exposed to the user and are accessible to the programmer [1].

## Chapter 3. GPUs for Extreme Computing – State-of-the-Art

With the emergence of extreme scale computing, modern GPUs have been extensively used in HPC applications like large data centers and supercomputers. The highly parallel nature of the GPU is attributed to its large number of compute cores and high-performance memory subsystems. We have GPUs from many different vendors. The most popular GPUs in the market are NVIDIA and AMD, which are used in high-performance computing. These two GPUs are different in many aspects with respect to the architecture, execution model, and memory hierarchy [23] [18].

#### 3.1 Evolution of GPUs

Graphics processing units were created with graphic and image processing in mind. Entertainment and game industries use GPUs extensively for building games with high-quality graphics. A huge revolution in the GPU programming industry was when GPU industries realized that we could use the available programming infrastructure for performing scientific applications. This was when NVIDIA came up with C-like programming language called CUDA targeting scientific computing in 2008 [15]. In almost same time, AMD came up with OpenCL programming language for (Accelerator processing unit) APUs.

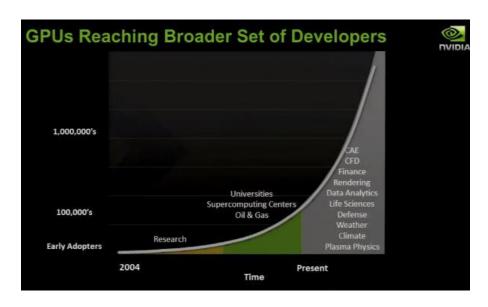

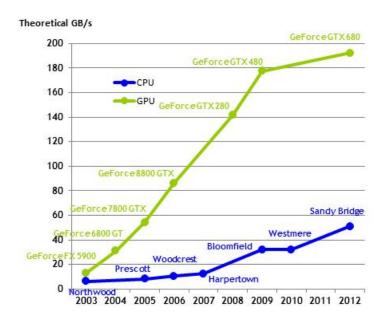

Figure 3.1: Trends in GPU Computing [15]

GPUs and their computing capabilities have changed over time, adding more computing power. In the gaming industry, these features enhance the user experience by adding rich graphics. The number of transistors in GPU hardware has increased drastically, providing increasingly advanced features in memory and execution models [15].

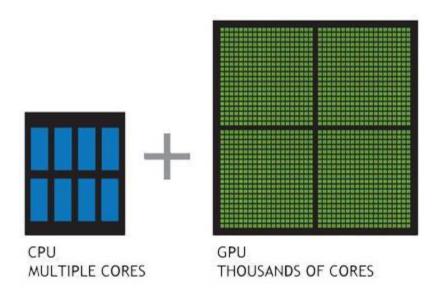

GPU computing tries to achieve the best performance by combining the power of both the CPU and GUP. CPUs are highly effective at making single threads go fast. Similarly, GPUs are excellent at creating thousands of threads and making all of them run really fast. In GPU computing, we combine the best computing capabilities of two worlds [18].

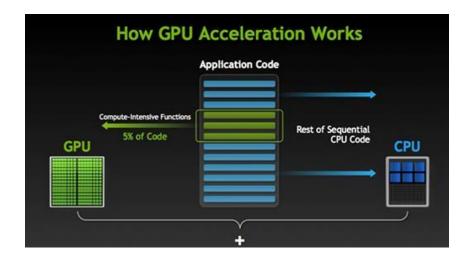

The basic idea behind GPU computing is running the majority of sequential code like file I/O, running the OS, and exchanging the data with sensors on the CPU. Then, we

identify the computationally intensive parts of the program, which are highly parallel, and run them on GPUs. This helps to exploit both CPU and GPU architectures efficiently [18].

Figure 3.2: Comparing CPU and GPU Compute Cores [18]

In GPU acceleration, we transfer the parallel code to the GPU, and the sequential code is run on the CPU. Being the host, the CPU controls how part of the program is transferred to the GPU, and how the results are collected again upon completion of the program by GPUs.

Figure 3.3: How GPU Acceleration Works [18]

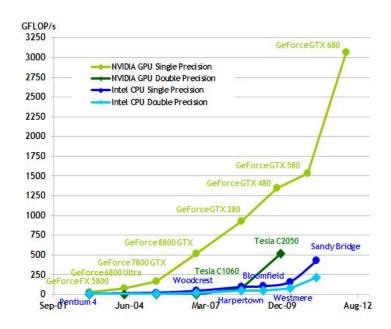

Per Moore's law, we have almost realized the highest performance, which can be drawn from the CPUs [15].

The new version of Moore's law of NVIDIA states, "As computers are not getting any faster they are just getting wider, parallel programming is here to stay". Because of this, data parallel computing is a more scalable solution for highly intensive applications [54].

These below graphs clearly indicate that parallel programming using GPUs will become the norm in the near future.

Figure 3.4: Floating-point Operations per Second for CPU and GPU [30]

Figure 3.5: Memory Bandwidth for CPU and GPU [30]

#### 3.2 NVIDIA GPUs

In recent years, the NVIDIA GPU has gained more popularity within the scientific computing fields because of language support provided for efficient programming and effective use of hardware.

#### 3.2.1 NVIDIA GPU Acceleration

There are three ways to accelerate applications for NVIDIA GPUs as shown in the figure below:

Figure 3.6: Three Ways to Accelerate Applications for NVIDIA GPUs [19]

GPU – Accelerated Libraries: In this approach, we use libraries in order to accelerate the application. This method does not require any special knowledge of GPU architecture or programming language. As the libraries are designed to provide a standard API format, they are conducive to high-quality performance with minimal code change. Some of the GPU libraries include cuDNN (for high-level machine-learning frameworks), cuFFT

(Fast Fourier Transform Library), cuBLAS-XT (Basic Linear Algebra Subroutine), and MAGMA (next-generation linear algebra) [19] [20].

**GPU Directives** – **OpenACC:** OpenACC provides compiler directives for parallel programming to run the code on CPUs, GPUs, APUs, and coprocessors. This directive around the parallel region will help move the computation to the accelerator and execute the instructions on the accelerator [19] [21]. One of the benefits of using OpenACC is that we can improve the performance drastically by spending significantly less time on understating and writing the code. OpenACC as a parallel programming model will be discussed in the upcoming chapters of this document.

CUDA Language: CUDA C or C++ is a C / C++ interface to the parallel programming on accelerators. CUDA provides an extension to the C / C++ language, allowing the programs to execute on GPUs using GPU threads. In CUDA, we write kernels that are meant to run using the GPU thread model. These kernels are the computationally intensive loops that we transfer to the GPU. In the meantime, we also have to transfer data to and from the CPU to the GPU, which is required for computation. Thus, data transfer and kernel writing are two critical tasks that the CUDA user should understand to get the most from GPUs. CUDA is one of the low-level programming languages for GPUs compared to OpenACC and to use of GPU libraries. Thus, coding in CUDA has a

learning curve that requires comparably more time to understand [19] [22]. We will discuss CUDA in a later section.

#### 3.2.2 Kepler Architecture

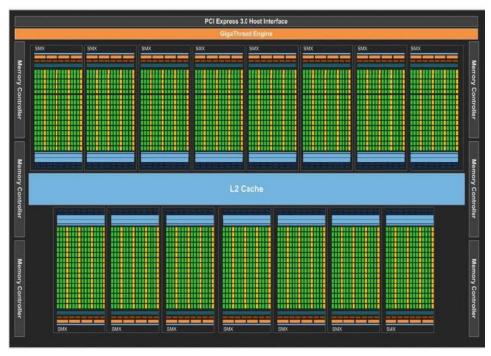

Kepler is one of the fastest and architecturally most complex microprocessors, with as many as 7.1 billion transistors. One of the greatest improvements over previous GPUs like Fermi is Kepler's superior power efficiency mechanism. Kepler provides over 1Tflop of a double precision throughput. A Kepler GK110 implementation includes 15 SMX units and six 64-bit memory controllers [24] [25].

Key features of the Kepler architecture include: 1. New SMX processor architecture, 2. Enhanced memory subsystem, 3. Hardware support for new programming models [24].

Figure 3.7: Kepler GK110 Full Chip Block Diagram [24]

### 3.2.2.1 Streaming Multiprocessor (SMX) Architecture:

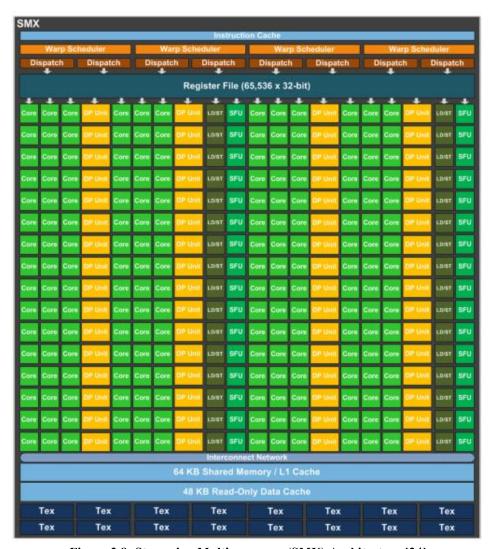

Each streaming multiprocessor has 192 single-precision CUDA cores, 64 double-precision units, 32 special function units (SFU), and 32 load/store units (LD/ST).

Figure 3.8: Streaming Multiprocessor (SMX) Architecture [24]

Each SMX unit contains 192 single-precision CUDA cores, each of which has a pipelined floating point and integer arithmetic logic unit. Kepler has exhibited significant performance improvement as a result of double precision operations as they are at the heart of HPC applications. Each SMX schedule threads in a group of 32 parallel threads, which are called warps. Each SMX has four warp schedulers and eight instruction

dispatch units, allowing four warps to be issued and executed concurrently. Kepler's quad warp scheduler selects four warps, and two independent instructions per warp can be dispatched at every cycle. The number of threads that can be accessed by the thread has been improved 4X times compared to Fermi [24].

Kepler implements a new shuffle instruction, which allows threads within a warp to share data. Atomic operations are an integral part of any HPC application. Kepler has improved throughput of global memory atomic operations by expanding native support for 64-bit atomic operations in global memory [24].

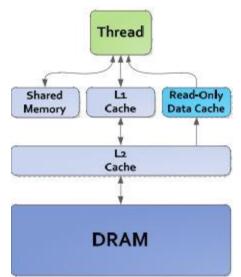

#### 3.2.2.2 Memory Subsystem

In Kepler GK110 every SMX has 64 KB of on-chip memory, which can be configured as 48 KB of shared memory with 16 KB of L1 cache or as 16 KB of shared memory with 48 KB of L1 cache. With Kepler, there is an additional flexibility in configuring the on-chip memory by permitting a 32KB/32KB split between the shared and L1 cache. In addition to the L1 cache, Kepler introduces a 48-KB cache for data that is known to be read-only for the duration of the function.

The Kepler GK110 GPU provides 1536 KB of dedicated L2 cache memory. The L2 cache is the primary point of data unification between the SMX units, servicing all load, store, and texture requests and providing efficient, high-speed data sharing across the GPU. The L2 cache on the Kepler offers up to twice the bandwidth per available clock in Fermi. Algorithms for which data addresses are not known beforehand, such as physics solvers, ray-tracing, and sparse matrix multiplication, especially benefit from the

cache hierarchy. Filter and convolution kernels that require multiple SMs to read the same data also benefit [24].

Figure 3.9: Kepler Memory Hierarchy [24]

Some of the new features in the Kepler GK110 are listed below. These features enable increased GPU utilization, making the parallel program design much simpler [24] [25].

**Dynamic Parallelism -** adds the capability for the GPU to generate new work for itself, synchronize results, and control the scheduling of that work via dedicated, accelerated hardware paths, all without involving the CPU. This capability allows less structured, more complex tasks run easily and effectively, enabling larger portions of an application to run entirely on the GPU. In addition, programs are easier to create, and the CPU is freed for other tasks [24] [25].

Hyper-Q - enables multiple CPU cores to launch work on a single GPU simultaneously, thereby dramatically increasing GPU utilization and significantly reducing CPU idle times. Hyper - Q increases the total number of connections (work queues) between the host and the GK110 GPU by allowing 32 simultaneous hardware - managed connections. Hyper - Q is a flexible solution that allows separate connections from multiple CUDA streams, from multiple Message Passing Interface (MPI) processes, or even from multiple threads within a process. Applications that previously encountered a false serialization across tasks, thereby limiting achieved GPU utilization, can realize a dramatic performance increase without changing any existing code [24][25].

Grid Management Unit – Enabling Dynamic Parallelism requires an advanced, flexible grid management and dispatch control system. The new GK110 Grid Management Unit (GMU) manages and prioritizes grids to be executed on the GPU. The GMU can pause the dispatch of new grids and queue pending and suspended grids until they are ready to execute, providing the flexibility to enable powerful runtimes, such as Dynamic Parallelism. The GMU ensures both CPU - and GPU - generated workloads are properly managed and dispatched [24] [25].

#### 3.3 AMD APUs

One of the biggest challenges in heterogeneous computing is memory management. In traditional architecture, CPUs and GPUs have different pools of memory with different

hierarchies. Computation on a GPU involves movement of data from system memory to GPU memory and back from the GPU to CPU after completing the computation. One of the biggest challenges in heterogeneous computing, especially GPU computing, is the movement of data between two architecturally different systems. Sometimes this negates the advantage of computing on GPU completely and adds more overhead.

AMD has been very keen to resolve the problems associated with data movements in heterogeneous computing. To address this problem and also to address different problems related to heterogeneous computing, AMD developed the Heterogeneous Systems Architecture (HSA). This architecture involves changes to the hardware platform as well as to software runtime systems.

### 3.3.1 Heterogeneous System Architecture

While computing in a heterogeneous environment, some of the challenges faced by programmers are very crucial to address. The primary concern in today's world is reducing power consumption. Consumers expect more longevity in batteries, for example, for many handheld and portable devices. Even the data centers, which process and store huge amounts of data, need cooling, which increases the cost of overall maintenance. Secondly, there is always a demand for improving the performance of current technology. Consumers naturally want their devices to handle increasingly greater volumes of data with reasonable performance. Finally, the productivity of the programmer is an important factor in using evolving hardware and software technologies. It should be easy for new programmers to tap into the capabilities of new architectures

without a considerable effort. One of the priorities of memory development should be the ability to run the same code on different platforms, targeting different devices without having to rewrite the code again and again for each specific platform [26].

HSA is one of the best comprehensive solutions for all the problems discussed. It promises improvement across all of the above parameters: power, performance, programmability, and portability [26].

The main goal of HSA design is to integrate the different processing elements tightly. HSA helps applications create and initialize data structures in a single unified address space to use the hardware effectively. The HSA model does not require fundamental changes to be implemented by software developers. Unified addressing used in HSA makes sharing of data between the CPU and GPU simple. The HSA architecture allows multiple compute tasks to work on the same coherent memory regions, using barriers and atomic memory operations, erasing the limitations associated with dissimilar memory systems [26].

The HSA Foundation aims to help system designers integrate different kinds of computing elements in a way that eliminates the inefficiencies of sharing data and sending work items between them. The HSA design allows multiple hardware solutions to be exposed to software through a common standard low-level interface layer, called the HSA Intermediate Language (HSAIL). HSAIL provides a single target for low-level software and tools. HSAIL is sufficiently flexible and yet low-level enough to allow each hardware vendor to map its individual underlying hardware design.. HSAIL frees the

programmer from the burden of tailoring a program to a specific hardware platform – the same code runs on target systems with different CPU/GPU configurations [26].

A very important feature of HSA is its simplification of the process of running applications on the architecture. HSA brings hardware to the application programmer. The different layers of HSA include hardware, interfaces, standard runtime components, and common intermediate languages. These layers work together to maintain memory coherence and work queues synchronized [26].

HSA is all about delivering improved user experiences through advances in computing architectures by providing improved power efficiency, performance, programmability, and portability [26].

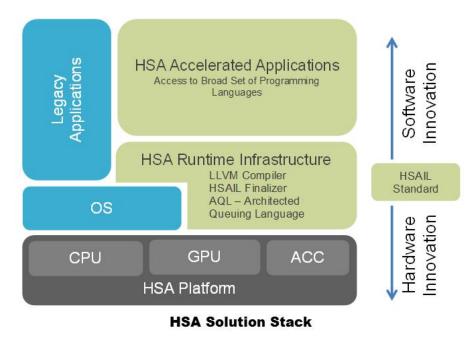

Figure 3.10: Heterogeneous System Architecture [26]

#### 3.3.2 Kaveri Architecture

AMD's most important leap towards the heterogeneous computing for HSA was heterogeneous Uniform Memory Access (hUMA). This architecture promises to solve this problem associated with the previous architecture. In hUMA memory space is cachecoherent which allows CPUs and GPUs use the same pointers to access the entire memory space. hUMA supports paged virtual memory, which makes it possible to work with larger data sets. This architecture allows the developer to write their applications using standard programming languages like Java, C++, and Python [28].

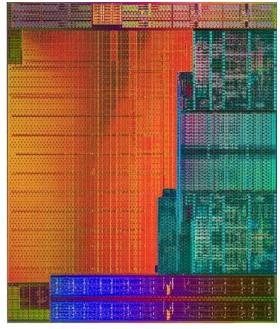

Kaveri is AMD's first processor to support hUMA. It has the new Steamroller CPU cores, combined with Radeon GCN (Graphics Core Next 2.0) architecture [29]. The main idea behind Kaveri is that current processors are too heavily CPU-biased. This technology utilizes the GPU core and draws on its maximum performance. Context switching between the CPU and GPU cores brings heavy overhead. Kaveri APUs are optimized to overcome this problem by increasing CPU frequencies, but these losses are buffered by a boost of almost 20% with new Steamroller cores [29].

Figure 3.11: Kaveri APU [29]

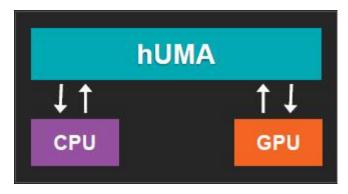

In Kaveri architecture, all the cores, CPUs, and GPUs, are called compute cores. Each compute core acts as a programmable hardware block that can run processes in its context and virtual memory space. The architecture contains four multi-threaded Steamroller CPU cores and eight GCN-based Radeon GPU cores. Two very important technologies which are implemented in Kaveri and HSA for making the computing possible on the cores are hUMA and heterogeneous Queuing (hQ) [29].

In Kaveri, using the hUMA memory access pattern allows both CPU and GPU access the same memory. hUMA reduces almost all the issues associated with data movement and data management on two different memory systems, which enhances the performance of the programs [29].

Figure 3.12: Block Diagram of Kaveri – hUMA [29]

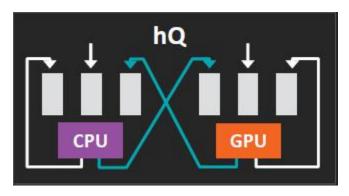

hQ is a very important element in Kaveri, as it allows the GPU to send its tasks to the queue, which can then be dispatched to the GPU or CPU. In the previously discussed architecture, the GPUs did not have any role in an event or work dispatch. This new feature increases performance by eliminating bottlenecks associated with latency in processing, leading to less power consumption. AMD claims that as these features are implemented in the architecture, programmers no longer have to write a code specific to the GPU [29].

The new HSA architecture features support for OpenCL 2.0 as a programming standard.

Figure 3.13: Kaveri hQ [29]

# **Chapter 4. Programming Models for Heterogeneous Systems**

Parallel programming models are the basis for drawing extreme compute parallelism from heterogeneous systems. These programming models help map parallel applications to the hardware of the compute elements, execute applications on hundreds of these devices, and finally produce results with high performance and greater accuracy. Development of parallel programming models has become a recent priority, as we are using large heterogeneous compute elements for application processing more than ever.

How do we decide which is the best programming model for a given application? There is no "best" model, although there are certainly better implementations involving some models compared to others.

Different parallel programming models have been designed not only to target GPUs, but especially to target accelerators in common, are OpenMP, CUDA, OpenACC, OpenCL, and OpenGL. We will discuss how each of these models work in providing the best strategies for writing parallel code for accelerator architectures.

#### **4.1 CUDA**

NVIDIA introduced CUDA at the end of 2006 as a parallel computing platform and programming model for general processing units [30]. NVIDIA's GPUs use CUDA to solve many complex computational problems more efficiently than CPUs. CUDA

provides a software environment for developers by allowing them to use C as a high-level programming language.

The three key abstractions provided by CUDA are a hierarchy of thread groups, shared memories, and barrier synchronization [30]. CUDA exposes all these features by providing a set of language extensions to C. These extensions allow CUDA to be a scalable programming language by running the programs on a number of multicores.

#### **Programming Model:**

CUDA provides fine-grained data parallelism and thread parallelism, which are nested within coarse-grained data and task parallelism. They also guide the programmer to partition the problem into coarse sub-problems that can be solved independently in parallel by blocks of threads. Each sub-problem is further divided into finer pieces, which can be solved cooperatively in parallel by all threads within the block. Some important elements of CUDA are discussed below.

**Kernels** are the main computational units that execute the code section on the GPU using CUDA C extensions. Kernels are executed N times by N CUDA threads. A kernel is defined using the \_\_global\_\_ declaration specifier, and the number of CUDA threads that execute the kernel is specified using a new <<<...>>> execution configuration syntax. Each thread that executes the kernel is given a unique *threadID* that is accessible within the kernel through the built-in *threadIdx* variable [30].

**Thread Hierarchy** is one of the important properties for CUDA programming. It specifies the level of parallelism applied to the loop, threadIdx is a three-vector component so that threads can be identified using a one-, two-, or three-dimensional thread index, forming a one-, two-, or three-dimensional thread block, respectively. This provides a natural way to invoke computation across the elements in a domain such as a vector, matrix, or volume [30].

In the following example, we add two matrices A and B of size NxN and store the result in matrix C:

```

// Kernel definition

__global__ void MatAdd(float A[N][N], float B[N][N], float C[N][N])

{    int i = threadIdx.x;

int j = threadIdx.y;

C[i][j] = A[i][j] + B[i][j];

}

int main()

{        ...

// Kernel invocation with one block of N * N * 1 threads

int numBlocks = 1;

dim3 threadsPerBlock(N, N);

MatAdd<<<numBlocks, threadsPerBlock>>>(A, B, C);

...}

```

Table 4.1: Code Snippet for Matrix Multiplication using CUDA [30]

There is an upper limit on the number of threads that can be spawned per block, and these threads of a block are expected to reside on the same processor core and must share the limited memory resources of that core. On current GPUs, a thread block may contain up to 1024 threads. However, the kernel can be executed by multiple equally shaped thread blocks so that the total number of threads is equal to the number of threads per block times the number of blocks [30]. The number of thread blocks in a grid is usually dictated by the size of the data being processed or the number of processors in the system.

The number of threads per block and the number of blocks per grid specified in the <<<...>>> syntax can be of type *int* or *dim3* [30]. Two-dimensional blocks or grids can be specified as shown in the example above.

Each block within the grid can be identified by a one-dimensional, two-dimensional, or three-dimensional index accessible within the kernel through the built-in blockIdx variable. The dimension of the thread block is accessible within the kernel through the built-in *blockDim* variable [30].

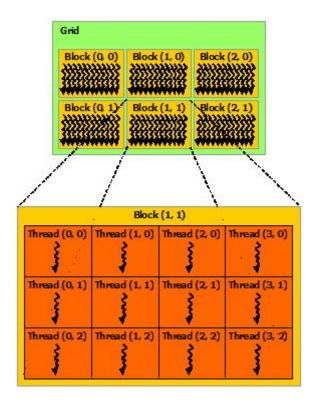

Figure 4.1: Grid of Thread Blocks [30]

Thread blocks are required to be executed independently: It must be possible to execute them in any order, in parallel or series. This independence requirement allows thread blocks to be scheduled in any order across any number of cores, enabling programmers to write code that scales with the number of cores. Threads within a block can cooperate by sharing data through shared memory and by synchronizing their execution to coordinate memory accesses. \_\_syncthreads() acts as a barrier at which all threads in the block must wait before any of them is allowed to proceed. For efficiency, the shared memory is expected to be low-latency, and \_\_syncthreads() is expected to be lightweight [30].

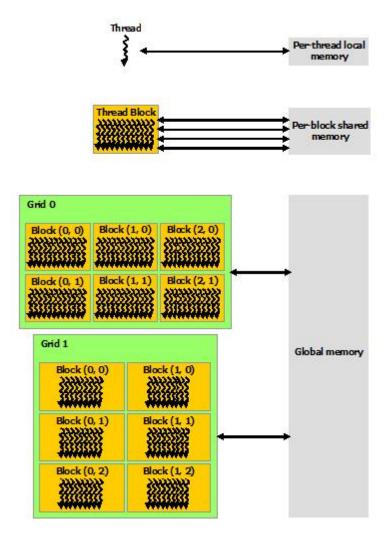

CUDA threads can access data from multiple memory spaces during their execution as shown in the figure below. Each thread has private local memory. Each thread block has shared memory visible to all threads of the block and with the same lifetime as the block. All of these created threads have access to the same global memory [30].

Figure 4.2: Memory Hierarchy [30]

### **Heterogeneous Programming**

The CUDA programming model assumes that the CUDA threads execute on a separate device connected to the main CPU via interconnect. This host and device execution model will have a different memory space, which needs to be allocated, deallocated, and synchronized.

### 4.2 OpenACC

OpenACC is a high-level directive-based programming model for accelerators that enables scientific and technical C, C++, and Fortran programmers to easily take advantage of the power of heterogeneous CPU/accelerator systems. This model provides a set of pragmas and high-level APIs for the non-native programmer hiding all the low-level details of the programming language compared to CUDA. OpenACC provides set of pragmas which serve as hints to the compiler regarding how different portions of the code should be run.

OpenACC allows programmers to use simple compiler directives to identify which areas of code to accelerate, without requiring modification to the underlying code itself. By identifying parallel code segments, OpenACC directives allow the compiler to perform the detailed work of mapping the computation on the accelerator.

Understanding the memory model and architecture of the systems will help the programmer to achieve better performance, as it helps to map the program to the hardware more efficiently.

**OpenACC Basic Syntax**: OpenACC supports C/C++ and FORTRAN languages for directive-based programming. Table 4.2 gives the syntax for C/C++ and FORTRAN.

| Syntax for C/C++                          | Syntax for Fortran                      |

|-------------------------------------------|-----------------------------------------|

|                                           |                                         |

| #pragma acc directive [clause [,] clause] | !\$ acc directive [clause [,] clause]   |

| Often followed by structured code block   | Often followed by structured code block |

|                                           | Paired with the matching end directive  |

|                                           | !\$ acc end directive                   |

Table 4.2: OpenACC Pragma's Syntax

The directives and clauses in italics can be replaced by appropriate implementations depending on the structure of the code. We can have only one directive on each line of code, which can be followed by more than one clause.

**Compute Constructs of OpenACC**: OpenACC API has two compute constructs namely 1. Kernels and 2. Parallel construct. Both constructs have the same goal, but they are used in different contexts.

1. Kernels Construct: When the kernels construct is applied to the loop nest, it is converted to parallel kernels by compiler to run efficiently on the GPU. This is a three-step process. The first step is to identify a parallelizable loop. The second is to map this abstract loop parallelism on to the concrete hardware parallelism. For NVIDIA GPU, this means mapping a parallel loop onto a grid-level or thread-level parallelism. In OpenACC, gang level parallelism is mapped to grid-level parallelism and vector parallelism mapped to thread-level parallelism. In the third step, the compiler has to generate and optimize the block of code to implement the selected parallelism. Hence, the kernels directive uses classical automatic parallelization to identify and parallelize the loops.

```

#pragma acc kernels

{

for( i = 0; i < n; ++i )

a[i] = b[i] + c[i];

}</pre>

```

**Table 4.3: Code Snippet for Sample Kernel Constructs**

**2. Parallel Construct:** OpenACC parallel construct tries to solve the same problem as that of the kernels directive. The only difference between the two is that the kernels construct is implicit, giving more freedom to the compiler to analyze the loop, find parallelism, and then map parallelism to the hardware threads. But in the case of parallel constructs, the compile command is more explicit. Whenever we use the parallel

construct, it is the programmer's responsibility to analyze the loop and determine when it is legal and appropriate to parallelize the loop.

```

#pragma acc parallel

{

#pragma acc loop

for( i = 0; i < n; ++i )

a[i] = b[i] + c[i];

}</pre>

```

Table 4.4: Code Snippet for Sample Parallel Constructs

**Loop clause:** An important observation from Table 4.4 is the use of the loop clause. Loop is a work-sharing construct. When we do not use the loop clause with the kernels/parallel directive, all the threads execute the code redundantly.

## 4.3 OpenMP

OpenMP is a high-level directive-based programming API for shared memory multiprocessor architecture, which uses incremental changes to the existing program to parallelize it. It includes a set of compiler directives/pragmas, library functions, and environment variables. OpenMP is sufficiently expressive and efficient for many applications. The directives used for parallelizing serve as compiler commands for C, C++, and FORTRAN languages. The main aim of the OpenMP model is improving the productivity of a programmer by accelerating the performance of the sequential code to get comparatively better performance [31]. A better understanding of the programming model and architecture of the target platform will help in implementing the right kind of optimization techniques to achieve better performance.

### 4.3.1 Memory Model of OpenMP

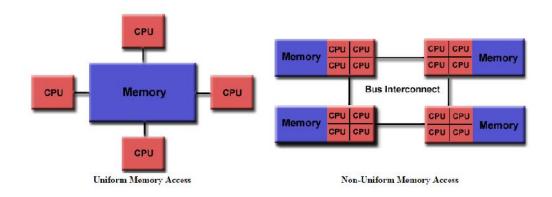

As indicated above, OpenMP is a programming model for shared memory multicore architecture.

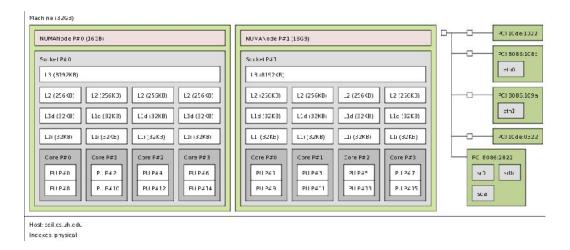

Figure 4.3: Memory Model for OpenMP [31]

In shared memory programming, each node is called a symmetric multi-processor (SMP), and these SMPs access memory simultaneously in order to provide communications among the processing elements. Compared to different heterogeneous memory subsystems, programming a shared memory system is relatively easy. This is because all SMPs share a single view of data and the communication between processors can be as fast as memory accesses to the same location. We can have systems with two different types of shared memory architecture: 1. Uniform memory access (UMA) as shown in Figure 4.3, where all SPMs share the same memory and the memory access time is the same for all cores. 2. Non-uniform memory access (NUMA) as shown in Figure 4.3 memory access time depends on memory system from which the processor is requesting the data [31].

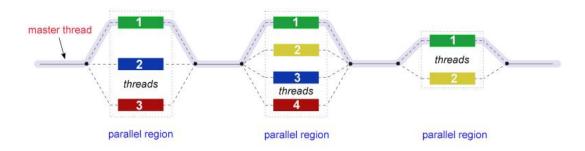

#### 4.3.2 Execution Model of OpenMP

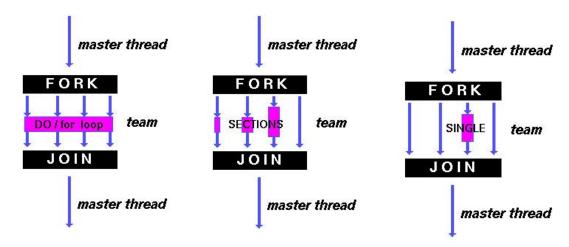

OpenMP uses the fork-join model for parallel execution. As shown in the figure below, the execution of the program starts with a single thread, which is the main/master thread created by the program. When the master thread encounters the parallel construct, it creates a team of threads to perform the computation in parallel. The number of threads created by the master thread depends on the value assigned to the environment variable OMP\_NUM\_THREADS or the number of threads provided, which is denoted as the routine *omp\_set\_num\_threads* (*number\_threads*) [31].

Figure 4.4: Fork-join OpenMP Execution Model [48]

## 4.3.3 OpenMP Programming Directives

OpenMP provides the compiler directives that can be inserted into the existing serial program. We have a slightly different syntax for using OpenMP pragmas in C/C++ and FORTRAN as shown in the Table 4.5 below.

| C/C++ directive format | <pre>#pragma omp parallel [clause] newline     if (scalar_expression)     private (list)     shared (list)     default (shared   none)     firstprivate (list)     reduction (operator: list)     copyin (list)     num_threads (integer-expression)</pre> |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | structured_block                                                                                                                                                                                                                                           |

| Fortran                | <pre>!\$OMP PARALLEL [clause]</pre>                                                                                                                                                                                                                        |

|                        | structured_block<br>!\$OMP END PARALLEL                                                                                                                                                                                                                    |

**Table 4.5: OpenMP Directive Usage**

Some important sets of directives for OpenMP API are described briefly in the following sections. The list is not exhaustive.

# **Parallel Region Construct:**

Parallel region construct is one of the most important parts of the OpenMP programming, as this construct is responsible for creating the threads that are, in turn, responsible for parallel programming. In the program, a single thread is executed until it meets the PARALLEL construct. Once the program encounters the PARALLEL

construct, it creates a pool of threads, and all these threads execute the upcoming block of code in parallel. Every thread executes each line of code in parallel until they encounter the implicit barrier at the end of the parallel clause [31]. After this point, the master thread takes over the execution as shown below.

```

int nthreads, tid;

/* Fork, a team of threads with each thread having a private tid variable */

#pragma omp parallel private(tid)

{

/* Obtain and print thread id */

tid = omp_get_thread_num();

printf("Hello World from thread = %d\n", tid);

/* Only master thread does this */

if (tid == 0)

{

nthreads = omp_get_num_threads();

printf("Number of threads = %d\n", nthreads);

}

} /* All threads join master thread and terminate */

```

**Table 4.6: Sample OpenMP Code Snippet**

#### **Work-sharing Constructs:**

Work-sharing constructs are very important, as they help in dividing work among all the threads, which are created using the PARALLEL construct. Work-sharing constructs do not create more or new threads. If we do not have the work-sharing constructs, and if we have only parallel constructs for a block, multiple threads will be created, but every thread executes the entire block of code. This will degradation the performance because

of the overhead associated with the construct itself. We have different types of worksharing constructs. Do/for constructs allow data parallelism by dividing the loop iterations among the threads. Sections' construct allows functional parallelism, as they allow different pieces of code to be executed by a single thread. The single construct is used to serialize the block or section of code; that is when we want some code to be executed by a single thread, we use a single construct [31].

Figure 4.5: Work-sharing Constructs [31]

#### **Nested Parallelism in OpenMP:**

OpenMP allows nested parallelism. When a thread executing in a team encounters one more parallel construct, the executing thread creates a group of threads and acts as a master thread. This feature allows parallelizing recursive algorithms in a natural way [2].

#### Task Parallelism:

The TASK construct defines an explicit task, which may be executed by the encountering thread, or deferred for execution by any other thread in the team. The data environment of the task is determined by the data-sharing attribute clauses. Task execution is subject to task scheduling. For more information on task scheduling and clauses, see the OpenMP 3.1 specification document [31].

```

!$OMP TASK [clause ...]

IF (scalar logical expression)

FINAL (scalar logical expression)

UNTIED

DEFAULT (PRIVATE | FIRSTPRIVATE | SHARED | NONE)

MERGEABLE

PRIVATE (list)

Fortran

FIRSTPRIVATE (list)

SHARED (list)

block

!$OMP END TASK

#pragma omp task [clause ...] newline

if (scalar expression)

final (scalar expression)

untied

default (shared | none)

mergeable

C/C++

private (list)

firstprivate (list)

shared (list)

structured_block

```

**Table 4.7: OpenMP Task Clauses**

### **Synchronization Constructs:**

Synchronization is a kind of inter-process communication that is required to maintain order and data dependencies in the program. PARALLEL has implicit synchronization at the end and in the beginning. DO, MASTER, and SINGLE constructs have implicit synchronization at the end of the construct. OpenMP provides a rich set of synchronization constructs like ATOMIC (to perform atomic operations), and FLUSH (provides point-to-point synchronization) [31].

### **Data Scope Attributes:**

Defining the scope of the variables is performed explicitly in OpenMP in order to ensure the correct results. As OpenMP is a shared memory programming model and many of the threads work on the same data, some variables change, and some should retain their values. Some variables should be the same for all threads, but some will have an updated value. All these conditions are taken care in OpenMP using the data scoping clauses explicitly. These overwrite the scoping provided by the programming environment / language. Data scoping is provided by PRIVATE, FIRSTPRIVATE, LASTPRIVATE, SHARED, DEFAULT, REDUCTION, and COPYIN constructs. These are used in conjunction with the PARALLEL constructs to define the data scope for the entire block

### 4.4 OpenCL

OpenCL is a programming language that helps in writing the programs for heterogeneous platforms. OpenCL routines are called *kernels*, which are executed on accelerators. OpenCL can be used to program, NVIDIA GPUs as well as AMD APUs. One of the biggest disadvantages of OpenCL is it has a significant learning curve compared to other heterogeneous programming languages.

### **Host Application Development:**

The first step in OpenCL programming is writing a host application. This program runs on the host and dispatches kernels to the coprocessor. This application can be programmed using C or C++, and every host application requires five data structures from OpenCL: cl\_device\_id, cl\_kernel, cl\_program, cl\_command\_queue, and cl\_context [33].

A host application distributes kernels to devices, and this kernel is represented by a cl\_kernel. The device receives kernels from the host represented by a cl\_device\_id. The host selects kernels from a program, which is represented by a cl\_program. Each device receives kernels through a command queue. In code, a command queue is represented by a cl\_command\_queue [33] [32]. The OpenCL context allows devices to receive kernels and transfer data. In code, a context is represented by a cl\_context.

# Chapter 5. Developing an Accelerator Benchmark Suite

The main goal of developing an accelerator benchmark is to evaluate an OpenACC model for heterogeneous computing. This benchmark also helps to understand how different clauses implemented in new OpenACC2.0 can be used to improve performance compared to OpenACC 1.0, CUDA, and OpenMP.

We have different programming models and standards like OpenCL, CUDA, and OpenMP, all of which support accelerator programming. OpenACC intends to achieve better portability across different accelerator architectures.

OpenACC code interoperates well with the broader ecosystem of libraries and parallel programming languages for accelerated development. Developers may choose vast majority of their application development with OpenACC.

We compare the performances of the benchmarks created using an accelerator benchmark suite with already existing accelerator models like CUDA and OpenMP.

Portability is of major concern while programming heterogeneous systems. Although there are low-level languages, such as CUDA, which is widely used to program GPUs, it is certainly not a portable approach. The main advantage of using CUDA is that it has more control over GPU architecture and offers programmers efficient programming techniques. Using OpenACC for accelerators is a viable approach while addressing the portability factor. In this work, we have certainly achieved portability by using OpenACC, but not the same performance as with a CUDA program. For example,

stencil code shows that the performance of the OpenACC code is ~77% of that of CUDA code. It may be acceptable to trade off higher productivity for lower performance as long as the performance of the high-level approach is not too low.

The OpenACC model is inspired by OpenMP; both are high-level programming model approaches. OpenACC as of today is more mature for accelerator programming compared to OpenMP. This helps in exploiting the massive capabilities of GPUs. Although the hardware used for OpenMP and OpenACC are significantly different from each other, comparative analysis between both models helps to understand how an OpenMP-like model, i.e. OpenACC, can be used efficiently for accelerators. The OpenMP 4.0 version, which was released recently, also adds support for GPU accelerators [42]. This comparison will help us in understanding how well OpenMP supports programming for GPU architecture.

### 5.1 Heterogeneous Benchmark Suite

There are various accelerator benchmarks created to compare and analyze the performance of applications with respect to runtime, power consumption, etc. We select the benchmarks, depending on the aim with which they are created and their usefulness with the given architecture.

#### 5.1.1 Overview

On using OpenACC for GPU programming, "Let me start by stating that OpenACC does not make GPU programming easy. You will hear some vendors or presenters saying that

OpenACC or some other language, library or framework makes GPU programming or makes parallel programming easy. Do not believe any of these statements. GPU programming and parallel programming is not easy. It cannot be made easy. However, GPU programming need not be difficult, and certainly can be made straightforward, once you know how to program and know enough about the GPU architecture to optimize your algorithms and data structures to make effective use of the GPU for computing. OpenACC is designed to fill that role." - Michael Wolfe, The Portland Group [35].

Background work involves understanding a different set of benchmarks, target architecture and intent of developing. Some benchmarks are listed in the section below.

SHOC Benchmark: The Scalable Heterogeneous Computing Benchmark Suite (SHOC) is a collection of benchmark programs that test the performance and stability of systems using computing devices with non-traditional architectures for general-purpose computing and the software used to program them. Its initial focus is on systems containing Graphics Processing Units (GPUs) and multi-core processors and on the OpenCL programming standard. It can be used on clusters as well as individual hosts [36].

In addition to OpenCL-based benchmark programs, SHOC also includes a Compute Unified Device Architecture (CUDA) version of many of its benchmarks for comparison with the OpenCL version. Multiple benchmark applications are written in both OpenCL

and CUDA. SHOC implements cluster-level parallelism with MPI. For multiple GPUs per node, SHOC provides node-level parallelism [37].

The SHOC benchmark suite is divided into two primary categories: stress tests and performance tests. The stress tests use computationally demanding kernels to identify OpenCL devices with bad memory, insufficient cooling, or other component problems [37]. The performance tests are further subdivided according to their complexity and the nature of the device capability they exercise.

Rodinia Benchmark: The Rodinia benchmark is published by the University of Virginia. A researcher desiring a set of GPU computing source codes to experiment with, but who does not need any kind of uniform scripting environment for code multiversioning, collecting performance, results, or changing platform settings across all benchmarks, may find the Rodinia benchmarks to be a better fit [34]. The Rodinia benchmarks have no compilation complexity other than standard source code and makefiles to understand. The support in Parboil provides easy solutions for conducting certain kinds of research experiments at the cost of a slightly more complex compilation and execution system. Rodinia is similar in philosophy and development of applications compared to the Parboil benchmarks. They contain a similar mixture of building-block kernels and applications, and also support both CUDA and OpenCL for most benchmarks [38].

# 5.2 Using OpenACC 2.0

OpenACC is an emerging high-level model available for GPU programming. It gained a lot of popularity in a very short period of time. We have some of the benchmarks that have implemented OpenACC versions. Porting applications using OpenACC1.0 are complicated, as they lack some key features. As OpenACC 1.0 did not have support for separate compilation units, it also lacked support for function calls as separate compilation units [14].

The rationale behind the release of OpenACC 2.0 was to enhance the productivity of programmers with more tools to enable them to write code and exploit the underlying GPU architecture.

Adding separate compilation unit is one of the most important features of OpenACC2.0. Function calls, which are very important elements of the programming language, are missing from the OpenACC 1.0 spec, because of the unavailability of the linkers to some targets. Thus, we needed to inline all the function calls in OpenACC 1.0 [41].

#### **5.2.1 Routine Directive**

Procedure calls and separate compilations are two of the most important features of any high-level programming language, as they allow modularity and also help in adding libraries and other components. OpenACC 1.0 did not support function calls from inside the parallel or the kernels region, as it lacked linker support. Thus, programmers must

manually inline the function calls in OpenACC 1.0. This was one of the main limitations of OpenACC 1.0 [35] [43].

OpenACC 2.0 introduces a new routine directive that enables calls to the routines to be made from within the compute region. This allows the compiler to build a host and device version of the function separately, allowing the device version to be called from the compute region. Using the routine directive, we can also specify the level of parallelism that should be applied to the called routine by inserting one of the gang, worker, vector, or seq clauses [43].

```

#pragma acc routine worker extern

#pragma acc routine worker

void matvec(float *v, float *x ,

void matvec(float *v, float *x ,

float *a, int i,int n);

float *a,int i, int n)

#pragam acc parallel loop gang

float xx=0;

for(int i=0;i<n;i++)</pre>

#pragma acc loop reduction(+:x)

for(int j=0;j<n;++j)</pre>

v[i]+=rhs[i];

xx+=a[i*n+j]*v[j];

matvec(v,x,a,i,n);

//procedure call on the device

x[i]=xx;

//in OpenACC 1.0 inlines the function

call

}

}

```

**Table 5.1: Usage of Routine Directive [35]**

#### **5.2.2 Nested OpenACC Regions**

Nested parallelism, which is introduced in OpenACC 2.0, allows kernel launches from within the kernels.

Dynamic parallelism and function calls complement each other. In the sense, when we have function calls on the GPUs, it is most likely that the function that is called

will also have structured loops that can be parallelized. If dynamic parallelism were not supported, then function calls would not have been very useful.

**Table 5.2: Nested Parallel Regions**

The goal of the routine calls and nested parallelism is to move as much code to the accelerator as possible. This allows decoupling of the device code from the host and reducing the data movements as much as possible.

#### **5.2.3 Unstructured Data Regions**

OpenACC 1.0 fostered structured data lifetimes, which are not always very practical because of the structure of the code. OpenACC 2.0 allows unstructured data lifetime for variables by implementing two new constructs: "acc enter" and "acc exit" clauses. Enter and exit data region clauses provide flexibility on how long the data can stay on the device or moved back to the host only when it is finally done. This will further reduce some of the unwanted data movements compared to the structured data movement and help overcome the bottlenecks associated with data transfer on the PCI bus. In C++ programming, we can relate the use of unstructured data with the use of constructors and

destructors, as data is created in one function and deleted in order. Thus, we can keep the data on the device longer. If there is no "exit data", then the lifetime of the variable continues until the end of the program [43].

```

class Matrix {

Matrix(int n) {

#pragma acc enter data

len = n;

copyin(a[0:n]) create(b[0:n])

v = new double[len];