©Copyright by Wenhao Chen 2014 All rights reserved

# HIGH SPEED MULTI-CHANNEL OPTICAL ROUTER DESIGN IN DENSE WAVELENGTH DIVISION MULTIPLEXING (DWDM) OPTICAL NETWORKS

#### A Dissertation

#### Presented to

the Faculty of the Department of Electrical and Computer Engineering

University of Houston

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

in Electrical Engineering

by

Wenhao Chen

August 2014

# HIGH SPEED MULTI-CHANNEL OPTICAL ROUTER DESIGN IN DENSE WAVELENGTH DIVISION MULTIPLEXING (DWDM) OPTICAL NETWORKS

| W                                                                   | Venhao Chen                                                                                    |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Approved:                                                           |                                                                                                |

|                                                                     | Chair of the Committee Dr. Yuhua Chen, Associate Professor Electrical and Computer Engineering |

| Committee Members:                                                  | Dr. E. Joe Charlson, Professor,<br>Electrical and Computer Engineering                         |

|                                                                     | Dr. Pauline Markenscoff, Associate Professor, Electrical and Computer Engineering              |

|                                                                     | Dr. Cumaraswamy Vipulanandan,<br>Professor,<br>Civil and Environmental Engineering             |

|                                                                     | Dr. Jaspal Subhlok, Professor, Computer Science                                                |

| Dr. Suresh K. Khator, Associate Dean, Cullen College of Engineering | Dr. Badri Roysam, Professor and Department Chair, Electrical and Computer Engineering          |

# Acknowledgements

First of all, I would like to thank my advisor, Dr. Yuhua Chen, who has been advising me in researches and experiments all these years towards my Ph.D. career. I would also like to thank her for putting great effort in my dissertation. During these four years in Systems Research Lab, Dr. Chen's professional attitude towards research as well as academic work has influenced me and her unique insight has helped me a lot in my Ph.D. study.

Secondly, I would like to thank my parents for raising me and bringing me to excellence. I could not have fulfilled my academic goals without their support and understanding along the way. Third, I would like to thank my wife who accompanies me and loves me unconditionally. Without comfort and advise from her during difficult times, I could not have gone this far today. Also, I would like to thank all of my lab members for their generous help and for creating a pleasant lab environment.

# HIGH SPEED MULTI-CHANNEL OPTICAL ROUTER DESIGN IN DENSE WAVELENGTH DIVISION MULTIPLEXING (DWDM) OPTICAL NETWORKS

An Abstract

of a

Dissertation

Presented to

the Faculty of the Department of Electrical and Computer Engineering

University of Houston

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

in Electrical Engineering

by

Wenhao Chen

August 2014

### **Abstract**

In the era of information explosions, the size and complexity of data is expanding dramatically. To meet this requirement, lots of efforts have been made in both the time domain and the frequency domain. In the wireless communication area, the prevalent Time-Division Multiple-Access (TDMA) used in second generation global system for mobile communications (GSM) network is a good example of manipulating the signal in the time domain in order to share bandwidth over time. Orthogonal frequency-division multiplexing (OFDM) on the other hand, utilizes orthogonal sub-carrier signals to carry data on parallel data channels, achieving high spectrum efficiency. On the optical link side, the Dense Wavelength Division Multiplexing (DWDM) is a promising solution to meet the requirement. By multiplexing different carrier wavelengths onto one single strand of fiber, the link bandwidth can increase exponentially.

But the all optical DWDM network is hard to utilize due to technology limitations. This dissertation aims at solving the current limitations on all-optical network from both switching technology and network architecture aspects. From the perspective of switching technologies, the DWDM Multi-Mode router provides an integrated platform to support three different switching technologies simultaneously. The dynamic reconfiguration capability in DWDM Multi-Mode enables the bandwidth sharing among three switching methods which increases the channel utilization. From the perspective of the applications, the Application-Aware (A<sup>2</sup>) optical network features the reverse data path reservation is a good candidate of asymmetric traffic transmission. By creating alternative switching technique towards optical switching network, the A<sup>2</sup> optical

scheduler eliminates the setup latency problem in traditional optical router. At the same time, the path reservation can be changed in real-time, increasing the probability of packets delivery.

The 3-D switching opened another dimension in optical network to reduce traffic blocking. A dynamical resource allocation scheme is proposed to assign bandwidth for different traffic flows. The hardware experiments showed the feasibility of the proposed 3-D switching and it is expected to serve as a building block of future optical networks.

# **Table of Contents**

| Ackno  | owledg  | gements                                                       | v   |

|--------|---------|---------------------------------------------------------------|-----|

| Abstra | act     |                                                               | vii |

| Table  | of Cor  | ntents                                                        | ix  |

| List o | f Figur | es                                                            | xii |

| List o | f Table | es                                                            | xv  |

| Chapt  | er 1    | Introduction                                                  | 1   |

| Chapt  | er 2    | Background                                                    | 7   |

| 2.1    | Ove     | erview of Dense Wavelength Division Multiplexing Technologies | 7   |

| 2.2    | Op      | tical Switching Network                                       | 8   |

| 2      | 2.2.1   | Overview of Switching Networks                                | 8   |

| 2      | 2.2.2   | Electrical Packet Switching (EPS)                             | 10  |

| 2      | 2.2.3   | Optical Circuit Switching                                     | 10  |

| 2      | 2.2.4   | Optical Packet Switching (OPS)                                | 11  |

| 2.3    | Op      | tical Burst Switching (OBS)                                   | 12  |

| 2      | 2.3.1   | OBS Networks Architecture                                     | 12  |

| 2      | 2.3.2   | Burst Assembly                                                | 14  |

| 2      | 2.3.3   | Burst Scheduling                                              | 16  |

| 2.4    | DW      | VDM Multi-Mode Switching                                      | 20  |

| 2      | 2.4.1   | Reconfigurable Multi-Mode Core Router Platform                | 21  |

| 2      | 2.4.2   | DWDM Multi-Mode Switching Networks                            | 22  |

| 2      | 2.4.3   | Multi-Mode Switching Router Architecture                      | 24  |

| Chap | pter | 3 Applic                | ation-Aware Dynamic Optical Switching                          | 28 |

|------|------|-------------------------|----------------------------------------------------------------|----|

| 3.   | 1    | Proposed A              | pplication-Aware (A <sup>2</sup> ) Optical Networks            | 29 |

| 3.   | 2    | Application             | -Aware Optical Path Setup                                      | 30 |

| 3.   | 3    | Application             | -Aware Optical Path Controller                                 | 35 |

| 3.   | 4    | A <sup>2</sup> Router I | nput Scheduler Design                                          | 38 |

| 3.   | 5    | Static and I            | Oynamic Service Grouping                                       | 43 |

| 3.   | 6    | Hardware P              | rototyping                                                     | 49 |

|      | 3.6  | 1 Prototy               | ping of router scheduler                                       | 49 |

|      | 3.6  | 2 Prototy               | ping of Dynamic Switching Optical Network                      | 50 |

|      | 3.6  | 3 Prototy               | ping of Application-Aware Optical Network                      | 52 |

|      | 3.6  | 4 Optical               | Signal Attenuation in A <sup>2</sup> Optical Switching Network | 54 |

| 3.   | 7    | Summary                 |                                                                | 55 |

| Chap | pter | 4 3-D Op                | otical Switch                                                  | 57 |

| 4.   | 1    | Motivation              |                                                                | 57 |

| 4.   | 2    | Proposed 3-             | D Switch                                                       | 59 |

| 4.   | 3    | Static 3-D S            | Switching                                                      | 66 |

| 4.   | 4    | Dynamic E               | levator Switching                                              | 68 |

| 4.   | 5    | Dynamic R               | econfigurable Router Controller Algorithm                      | 71 |

| 4.   | 6    | 3-D Elevato             | or Switch Edge Router Design                                   | 76 |

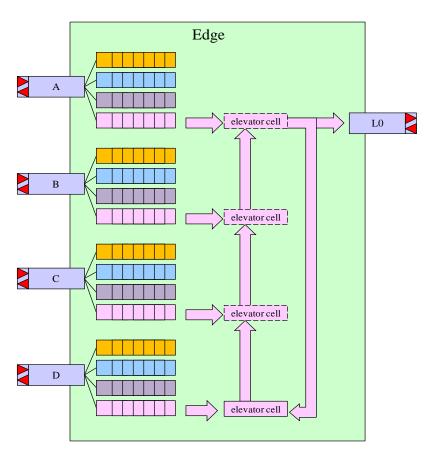

|      | 4.6  | 1 Client                | Cell Module Design                                             | 77 |

|      | 4.6  | 2 Networ                | k Cell Module Design                                           | 78 |

|      | 4.6  | 3 Elevato               | or Cell Module Design                                          | 78 |

|      | 46   | 4 Formal                | Notation of 3-D Elevator Switch                                | 80 |

| 4.7      | Sur  | nmary                                          | . 84 |

|----------|------|------------------------------------------------|------|

| Chapter  | 5    | Hardware Prototyping of the 3D Elevator Switch | . 85 |

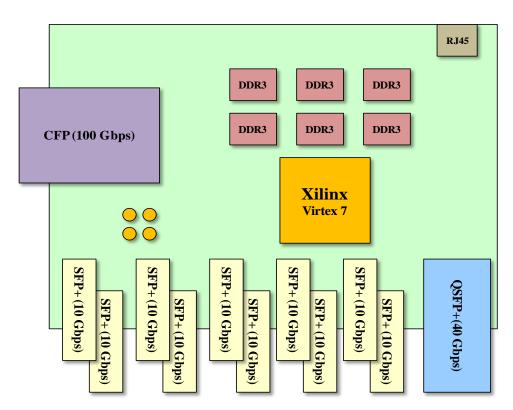

| 5.1      | 100  | G Edge Single Channel Design                   | . 85 |

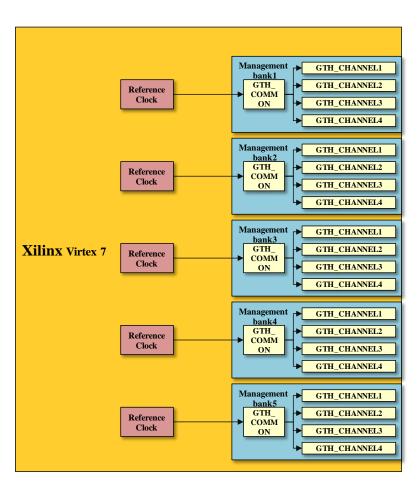

| 5.1      | .1   | Xilinx Virtex 7 Board                          | . 85 |

| 5.1      | .2   | Xilinx Virtex-7 GTX Transceivers               | . 87 |

| 5.1      | .3   | Hightek Xilinx Virtex-7 Evaluation Board       | . 89 |

| 5.1      | .4   | Hightek Systems Transceiver Core               | . 90 |

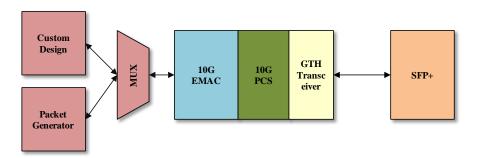

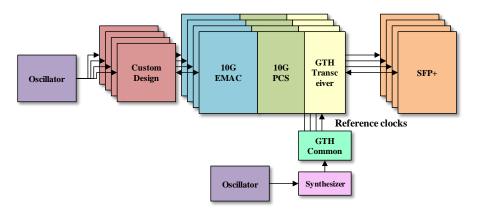

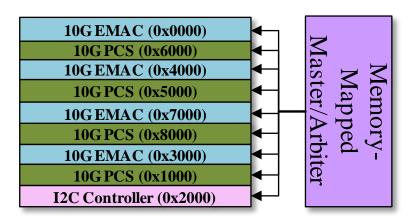

| 5.1      | .5   | Elevator Switch Peripheral System Design       | . 92 |

| 5.2      | Par  | ameterized Elevator Module                     | . 96 |

| 5.2      | .1   | Integrate the Parameterized Elevator Module    | . 99 |

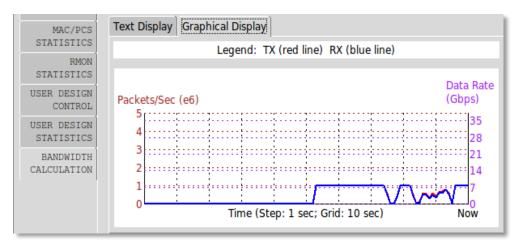

| 5.3      | Haı  | rdware Experiment                              | 100  |

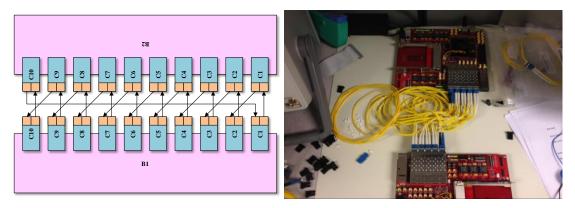

| 5.3      | .1   | Configuration 1 (3-in-1-out)                   | 100  |

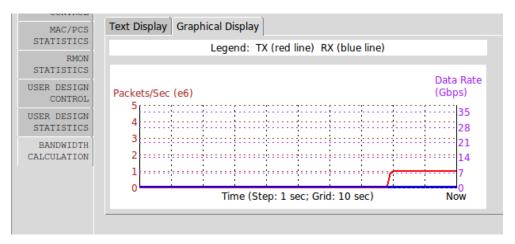

| 5.3      | .2   | Configuration 2 (3-in-3-out)                   | 101  |

| 5.3      | .3   | Configuration 3 (9-in-9-out)                   | 104  |

| 5.4      | Sur  | nmary                                          | 106  |

| Chapter  | 6    | Conclusion                                     | 107  |

| Bibliogr | aphy | y                                              | 109  |

# **List of Figures**

| Figure 1: current switching network hierarchy                                             | . 9 |

|-------------------------------------------------------------------------------------------|-----|

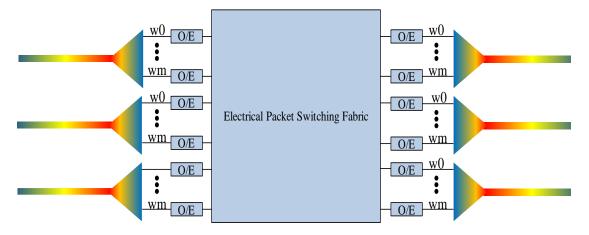

| Figure 2: Electrical Packet Switching architecture                                        | 10  |

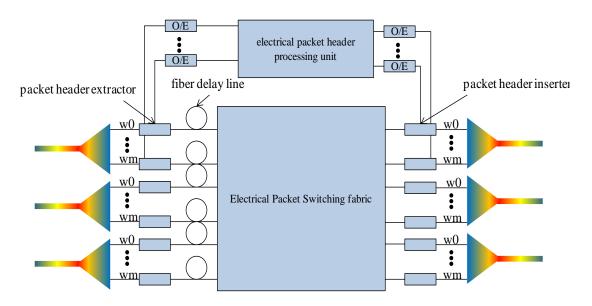

| Figure 3: Optical Packet Switching architecture                                           | 12  |

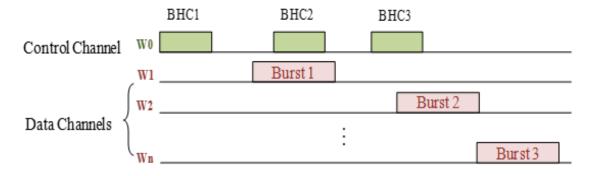

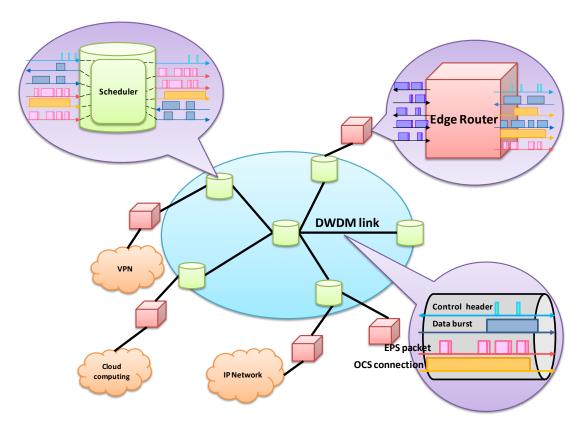

| Figure 4: relationship between BHC and Data Burst in OBS                                  | 13  |

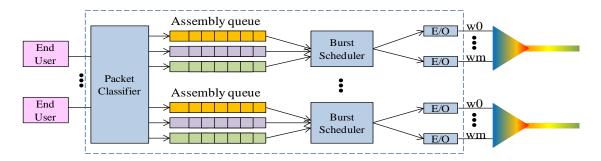

| Figure 5: OBS edge router architecture                                                    | 14  |

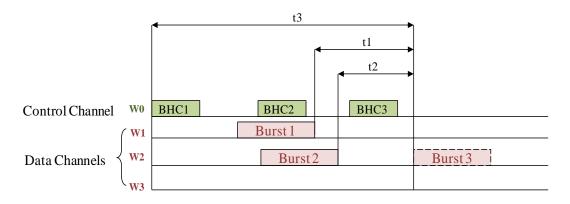

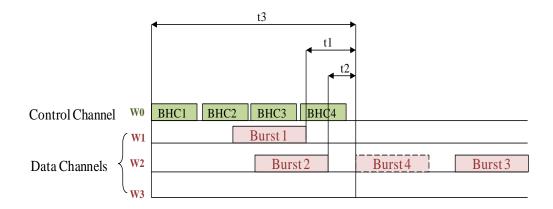

| Figure 6: OBS JET and JIT scheme                                                          | 17  |

| Figure 7: LAUC scheduling algorithm in OBS router                                         | 18  |

| Figure 8: LAUC-VF scheduling algorithm in OBS router                                      | 19  |

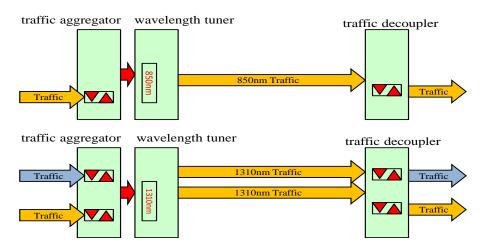

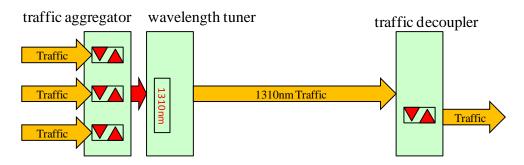

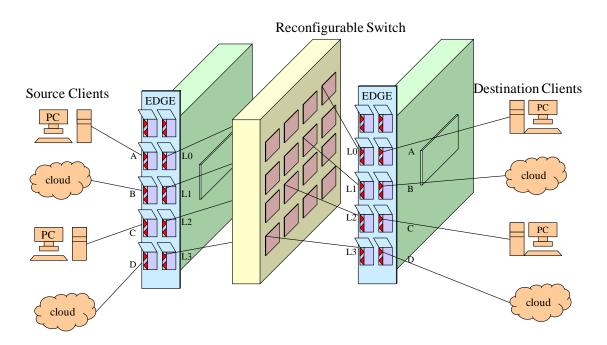

| Figure 9: DWDM Multi-Mode switching network                                               | 23  |

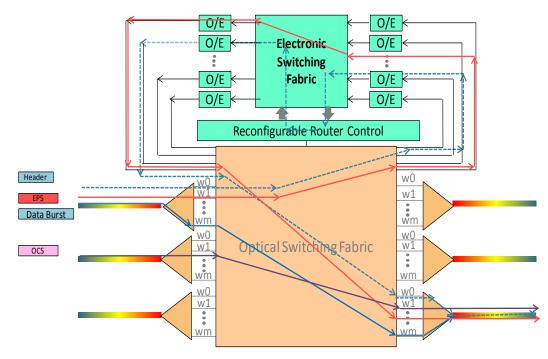

| Figure 10: Multi-Mode switching in core router                                            | 24  |

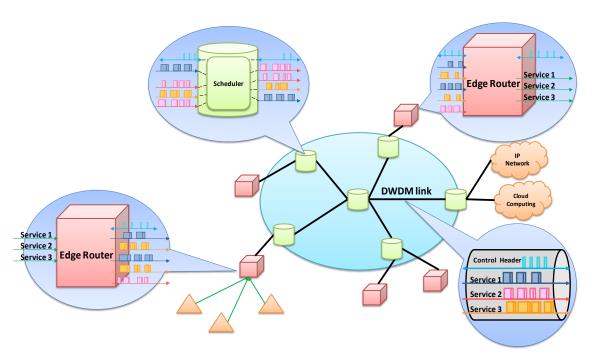

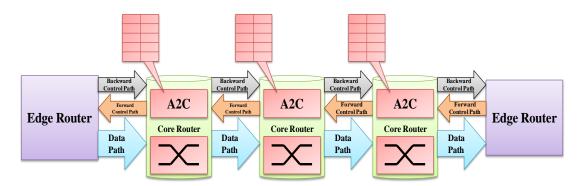

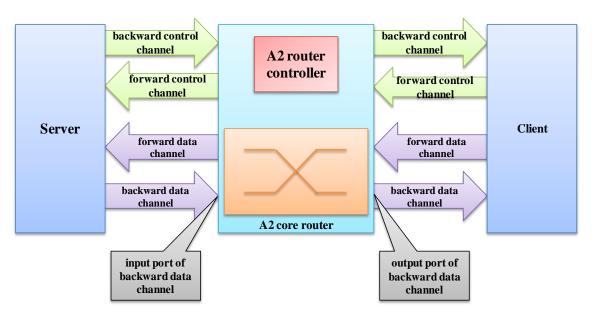

| Figure 11: A <sup>2</sup> Dynamic optical switching networks                              | 29  |

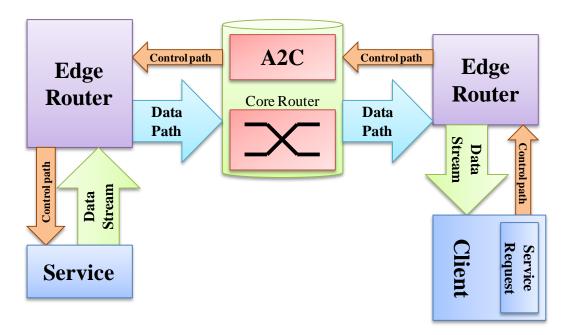

| Figure 12: application-aware optical path setup architecture                              | 32  |

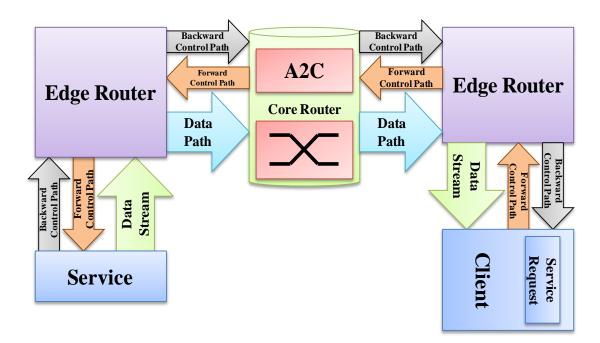

| Figure 13: reverse path reservation                                                       | 33  |

| Figure 14: Path reservation of casacated core routers                                     | 35  |

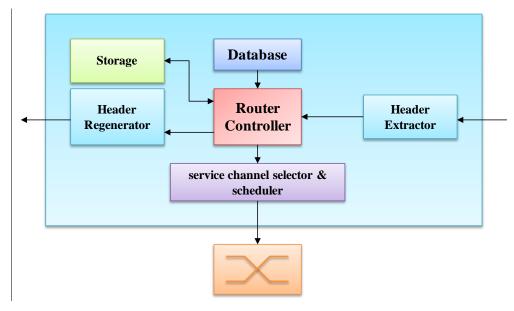

| Figure 15: blockdiagram of the A <sup>2</sup> C in A2 router                              | 36  |

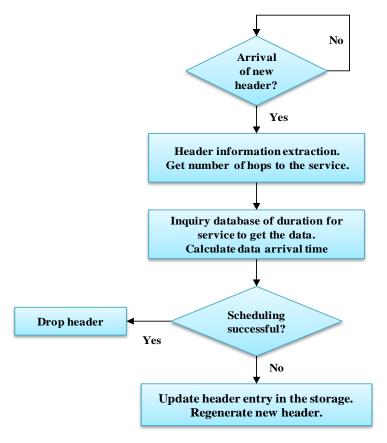

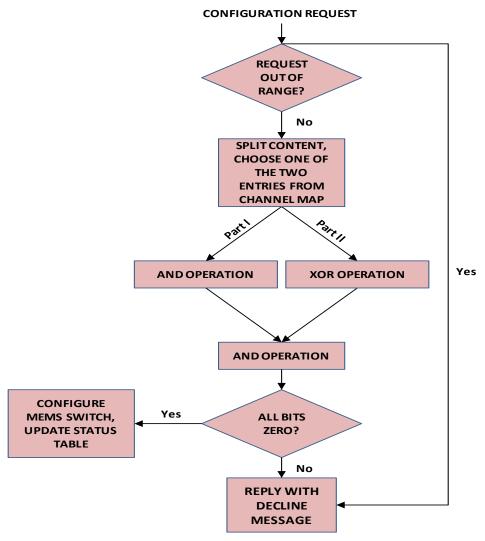

| Figure 16: flow chart of reverse path reservation                                         | 37  |

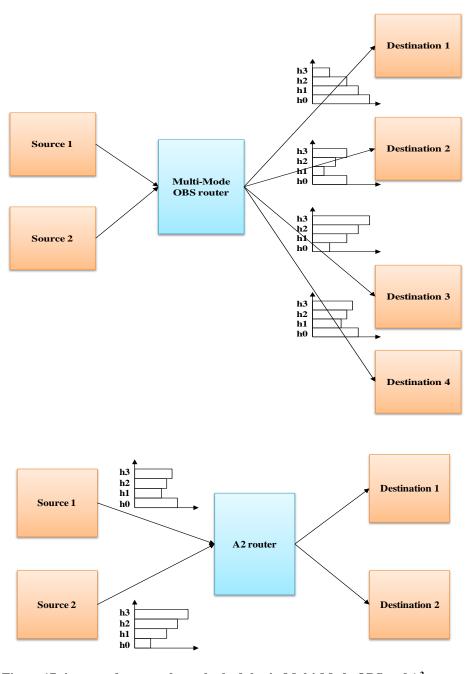

| Figure 17: input and output channel scheduler in Multi-Mode OBS and A <sup>2</sup> router | 38  |

| Figure 18: Reverse path reservation                                                       | 40  |

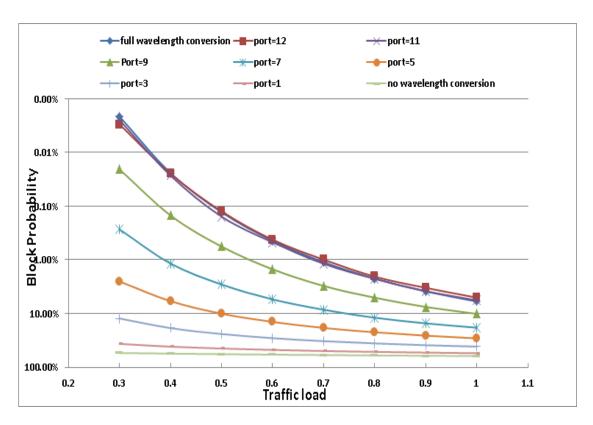

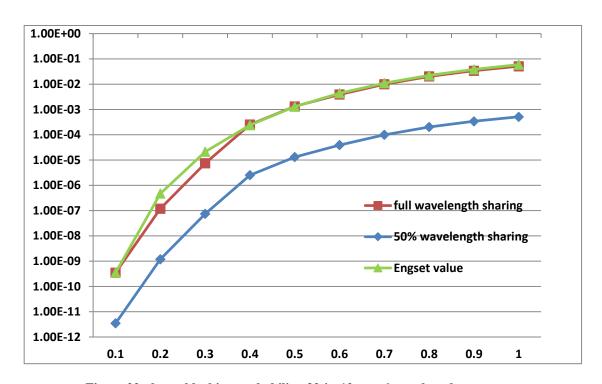

| Figure 19: burst blocking probability versus number of O/E/O ports assigned               | 44  |

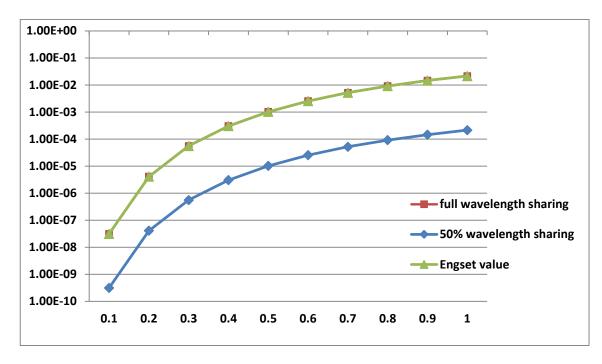

| Figure 20: burst blocking probability. 12-in-8-out, 4 wavelength converters               | 46  |

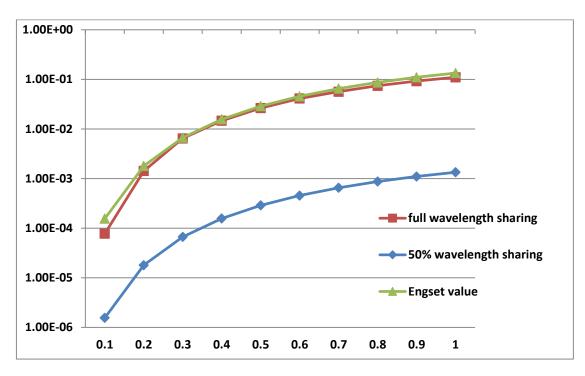

| Figure 21: burst blocking probability, 8-in-4-out, 2 wavelength converters                | 46  |

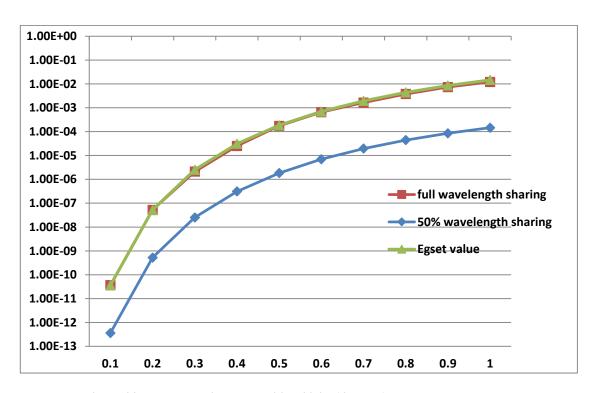

| Figure 22: burst blocking probability. 32-in-12-out, 6 wavelength converters             | 47 |

|------------------------------------------------------------------------------------------|----|

| Figure 23: burst blocking probability. 20-in-12-out, 6 wavelength converters             | 47 |

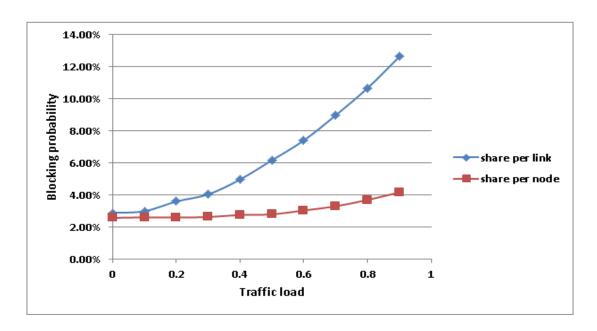

| Figure 24: burst blocking probability in shaer per link and share per node configuration | 48 |

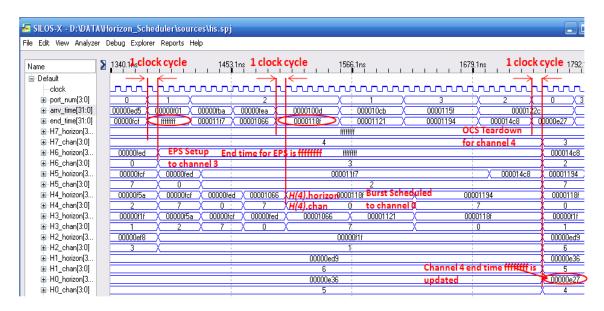

| Figure 25: circuit simulation for concurrent EPS, OCS and OBS burst scheduling           | 49 |

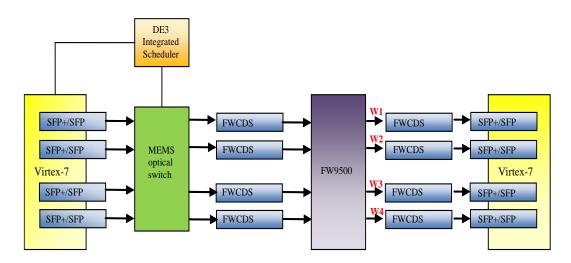

| Figure 26: hardware testbed with integrated scheduler controlling custom-built MEMs      | 50 |

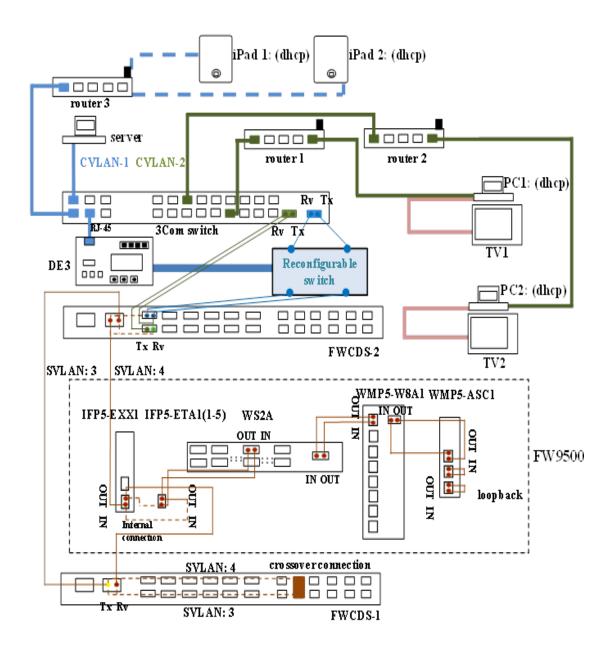

| Figure 27: system architecture of application triggered dynamic optical path setup       | 53 |

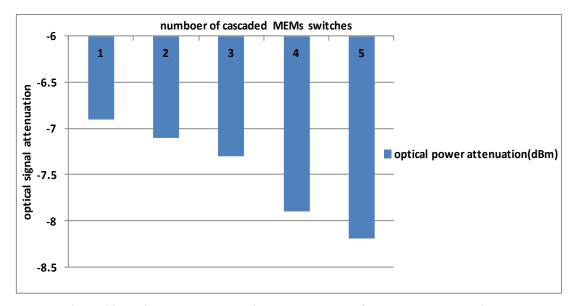

| Figure 28: optical power attenuation measurement of cascaded MEMs switches               | 55 |

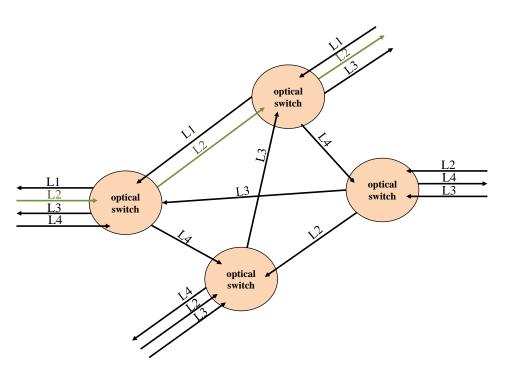

| Figure 29: optical switching system                                                      | 58 |

| Figure 30: example of two traffic stream with one destination                            | 59 |

| Figure 31: example of multiple traffic streams with one destination                      | 60 |

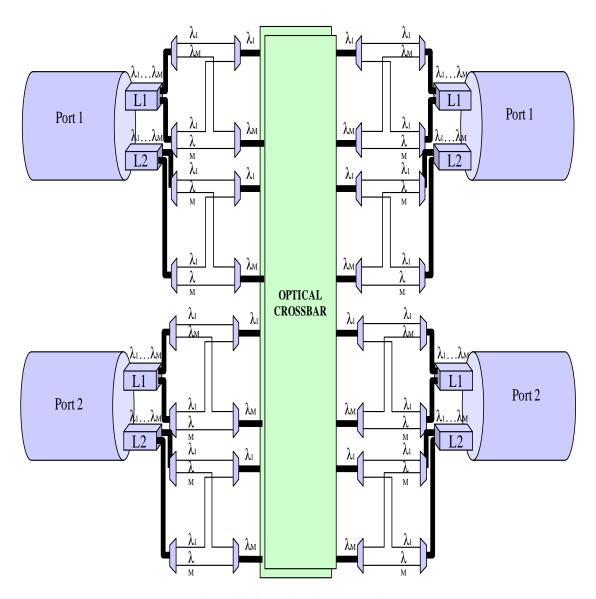

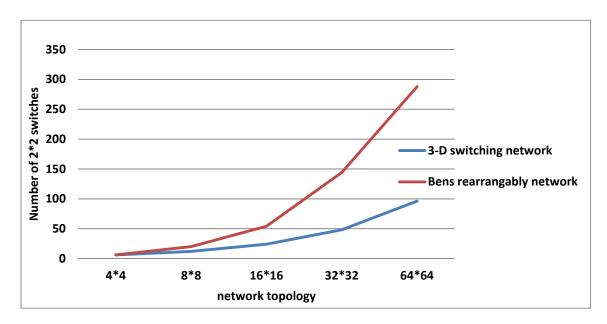

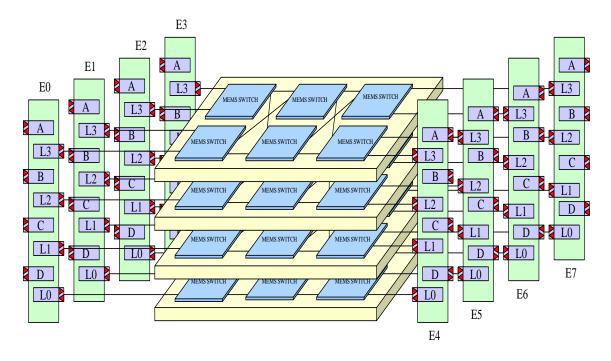

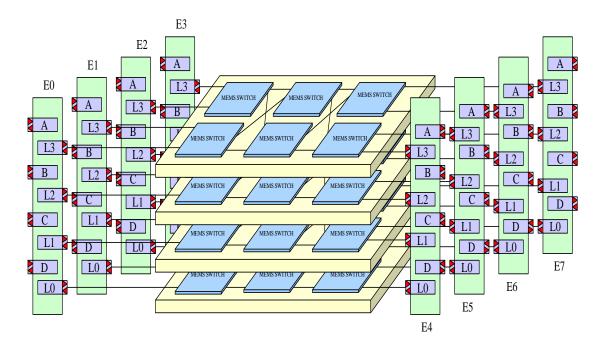

| Figure 32: 3-D switching system                                                          | 61 |

| Figure 33: 3-D switching block diagram                                                   | 64 |

| Figure 34: static pipelined switching system                                             | 66 |

| Figure 35: MEMs switches usage comparison between bens network and proposed 3-D          |    |

| network                                                                                  | 67 |

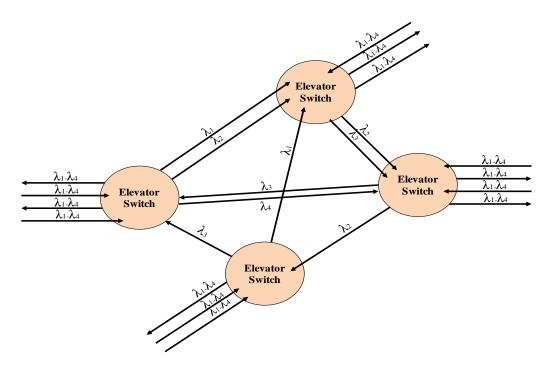

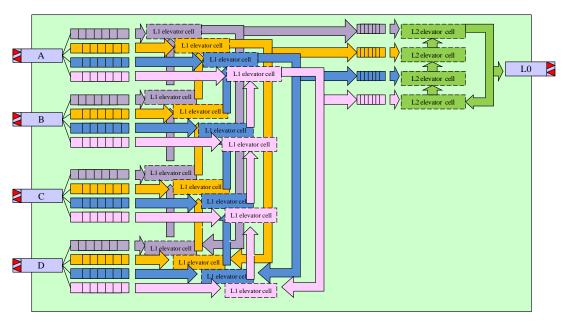

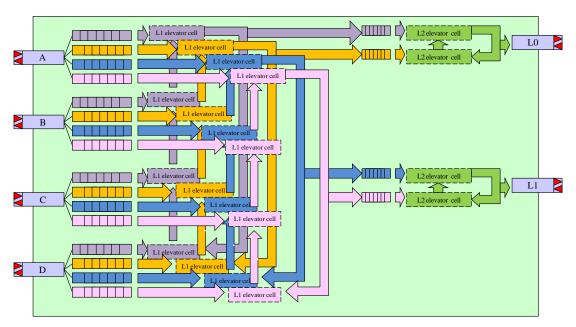

| Figure 36: Overview of elevator switching architecture                                   | 68 |

| Figure 37: Overview of 3-D switching architecture                                        | 69 |

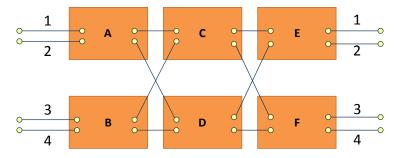

| Figure 38: 4x4 non-blocking sub-switching system                                         | 71 |

| Figure 39: Flowchart of Controller Configuration Algorithm                               | 76 |

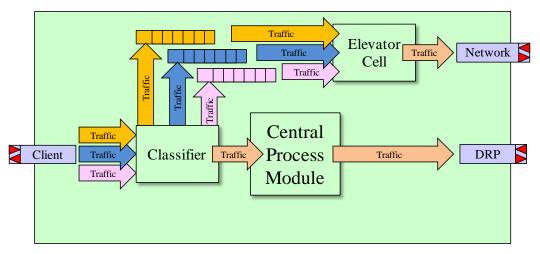

| Figure 40: client cell block diagram                                                     | 78 |

| Figure 41: elevator cell block diagram                                                   | 79 |

| Figure 42: elevator cell block diagram                                                   | 82 |

| Figure 43: elevator module extended block diagram                                        | 83 |

| Figure 44: Xilinx Virtex 7 GTH transceiver Block Diagram                              |

|---------------------------------------------------------------------------------------|

| Figure 45: HG707 Evaluation board Block Diagram                                       |

| Figure 46: HG707 GTX Transceiver Core                                                 |

| Figure 47: overview of top-level 3-D elevator switching system                        |

| Figure 48: AXI4-Lite Master/Arbiter address space                                     |

| Figure 49: single channel operation                                                   |

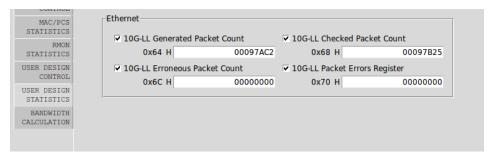

| Figure 50: error register status                                                      |

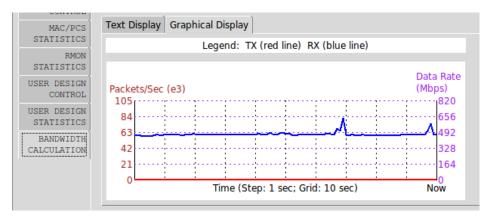

| Figure 51: PC traffic throughput                                                      |

| Figure 52: daisy chain experiment configuration                                       |

| Figure 53: channel 4 traffic monitor status                                           |

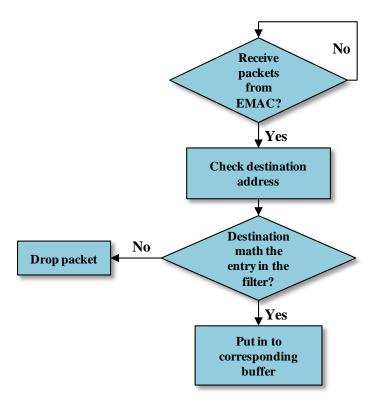

| Figure 54: traffic filter flow chart                                                  |

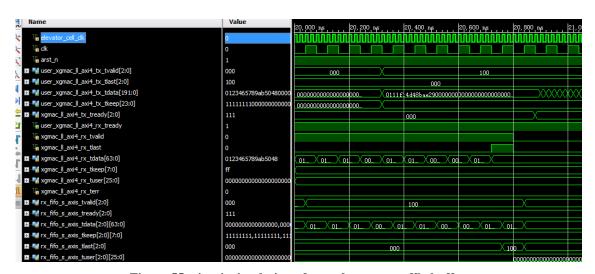

| Figure 55: circuit simulation of asynchronous traffic buffer                          |

| Figure 56: elevator switching internal system design                                  |

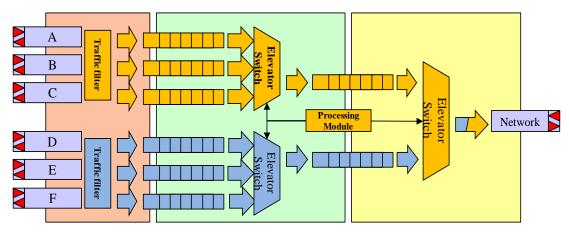

| Figure 57: 3-in-1-out elevator switching system hardware configuration                |

| Figure 58: real-time traffic at port D                                                |

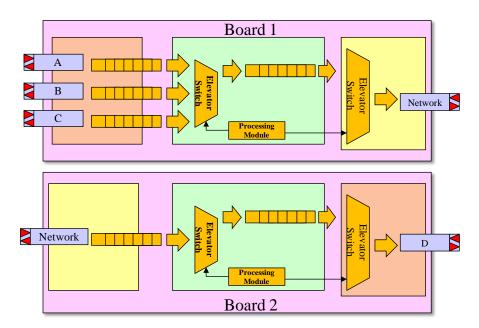

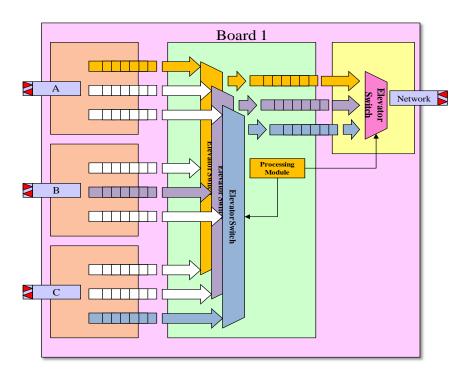

| Figure 59: 3-in-3-out elevator switching system hardware configuration on board 1 102 |

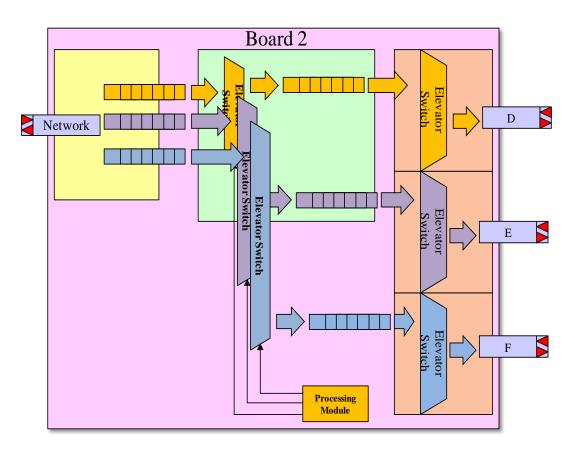

| Figure 60: 3-in-3-out elevator switching system hardware configuration on board 2 103 |

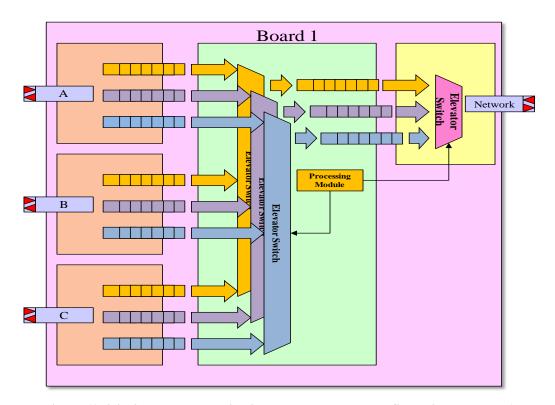

| Figure 61: 9-in-9-out elevator switching system hardware configuration on board 1 105 |

# **List of Tables**

| Table 1: wavelengths bands and corresponding transmission window | 8  |

|------------------------------------------------------------------|----|

| Table 2: optical power measurement                               | 54 |

| Table 3: 16x16 elevator switching routing table                  | 70 |

| Table 4: 16x16 elevator switching request entry                  | 72 |

| Table 5: 16x16 elevator switching channel map table              | 73 |

| Table 6: 16x16 elevator switching status table                   | 74 |

# **Chapter 1 Introduction**

Since the birth of Internet, Internet has undergone through a huge expansion worldwide. From the very beginning, the Internet was very sparse due to the equipment limitations and political issues. However, a campaign in 1982 to increase the awareness of information technology in UK lasted for 12 months and eventually it marked the acceptance of IT to general public. At the same time, a standardized Internet protocol Transmission Control Protocol/Internet Protocol (TCP/IP) came out in 1982 and it represents the introduction of the Internet.

The data transmission traffic has expanded 45-50 percent a year since the debut of the Internet. Since 1982, the speed of wide area network (WAN) modems have increased from 64 Kbps to 200 Mbps; the speed of Ethernet local area networks (LAN) have reached 100 Gbps versus 10 Mbps in 1981 and mobile data reaches the speed of 50Mbs which is forty thousand times faster than the speed in 1981. On one hand, the development of manufacturing technology has almost driven the device speed increase exponentially each year. Thanks to the rapid development of very large scale integrated circuit (VLSI), the PCs and mobile devices such as tablet, smart phone have become necessities in daily lives and they stimulate the development of more and more multimedia applications to enrich people's life. Nowadays, people are more and more likely to use Internet to stream videos, movies, to make phone calls through Voice over IP (VoIP), and to play online games with friends. However, these network applications running on their devices require tremendous bandwidth and they have brought tremendous traffic load into the network. Global Internet usage through mobile device is

growing remarkably. As shown in statistics, the number of global mobile users in 2012 was 1.3 billion versus 1.5 billion desktop users. But this 10% gap is filled in merely two years: In 2014, mobile devices accounted for 55% of Internet usage in the United States in January. Applications occupy 47% Internet bandwidth while 8% traffic comes from mobile browsers. Furthermore, the Internet faces new bandwidth challenges toward supporting the prevalent cloud computing and distributed data processing technology since these services requires high bandwidth in order to corporate with others and update the database frequently.

To support novel applications and accommodate services on the network side, service providers try to accommodate existing equipment and configurations while achieving high traffic throughput. This can be done by upgrading existing devices, upgrading backbone networks as well as adding more flexible switches and advanced traffic management schemes. However, any performance enhancement needs to take cost into consideration and the balance between performance enhancement and cost becomes a major issue which the service providers would concern. On the client's side, various applications and even sessions within applications require different latency and jitter performance. It is an intuitive idea to put different traffic streams that have different priorities onto different transmission lines, but these lines have to have the capability of fast dynamic configuration to better serve end users in order to achieve Quality of Service (QoS) guarantee.

DWDM technology multiplexes a number of optical carrier signals onto a single optical fiber by using different wavelengths of laser light and this technique enables massive bandwidth expansion over one strand of fiber. The DWDM allows hundreds of

wavelengths to carry signal each at 100Gbps which is considered an ultimate solution for backbone networks. However, to build an agile network and to provide flexibility in traffic manipulation and management, DWDM requires sophisticated switching and routing schemes between edges. The vendor needs switching technologies to decouple wavelength at certain nodes and to couple information onto other wavelengths. By doing this, wavelength can be dropped and added at any node, which achieves the purpose of exchanging information.

Currently there are three switching technologies existed in the core routers. They are Optical Circuit Switching (OCS), Electrical Packet Switching (EPS) and Optical Burst Switching (OBS). In optical circuit switching, before sending the data message, a path is explicitly set up between the source and the destination. This mechanism has the distinct advantage of guaranteed bandwidth. However, it suffers from severe bandwidth underutilization in the absence of data between the source and destination pairs. In order to address the inefficient resource utilization problem in OCS, EPS breaks down messages into packets and core routers decide the next hop these packets would go through. This technology deploys statistical multiplexing and it makes full use of the bandwidth. Furthermore, the in-sequence arrival of packets is not required in EPS. Although similar concepts can be used to realize optical packet switching, an all optical packet switched network is very hard to utilize for two reasons. For one thing, the core router needs to decode the optical packet header and then decides the next hop of the packet. This has to be implemented in the electrical domain which indicates the signal has to be converted from the optical signal into the electrical signal at each ingress port, and it needs to be converted back to the optical domain at the egress port after the packet is

processed. The expensive optical to electrical (O/E) and electrical to optical (E/O) converters are not scalable to be massively deployed in DWDM networks considering the exorbitant price service providers would have to pay. Moreover, optical packet payload needs to be buffered optically while the packet header is being processed. As a result, all optical packet switching is not commercially viable with the current technology.

OBS on the other hand is considered a prominent candidate towards future optical network. In OBS, packets are aggregated into the burst based on destinations, and forwarded on DWDM links. There is no O/E/O (optical to electrical and electrical to optical) conversion at each hop. However, traditional OBS lacks of packet level traffic management in the sense that the traffic is groomed according to the destination address based on the first come first serve criteria. Hence, packets lost their own identity after the data burst is formed. To maintain the packet identity observable is a big challenge in traffic management. Traditionally, adjusting the burst assembling time and the burst length would mitigate the priority issue to some extent. However, in packets with different QoS levels that have the same destination scenario, this mechanism will have limited influence on the jitter management.

This dissertation first analyzes the advantages and disadvantages of the above mentioned switching technologies. Based on the investigations, new network architecture is proposed and discussed to accommodate the fast growing Internet. In Chapter 2, an overview of optical communication systems is provided including DWDM optical switching technologies, three different optical switching types (EPS/OCS/OPS) and their specific signaling in the optical network. A detailed literature review of OBS network such as the burst assembly schemes and burst scheduling mechanisms are discussed. The

Multi-Mode optical switching network which provides a unified approach towards heterogeneous traffic is also discussed in Chapter 2, with illustrations of the function of Multi-Mode router to demonstrate the concurrent support of different switching modes.

The Application-Aware ( $A^2$ ) Dynamic Optical Switching is proposed in Chapter 3 to address the problem of asymmetric traffic flow in optical network systems. Furthermore, the architecture and scheduler design of the  $A^2$  Switch are demonstrated to show the complete network design. In addition to software simulation on the performance of the proposed  $A^2$  optical switch, the hardware testbed verification from the aspect of signal attenuation and optical path setup are also provided in Chapter 3 to demonstrate the feasibility of the proposed  $A^2$  optical switching.

3-D optical switch architecture is proposed in Chapter 4 to address the traffic blocking issue while maintaining high throughput by adding another dimension to existing optical switching network. This proposed technique changes the optical network fundamentally and the traffic block probability is expected to decrease through the utilization of the 3-D switching architecture. Two variations toward the implementation of the 3-D Optical Switching, namely, Static Elevator Switching and Dynamic Elevator Switching, are also discussed in Chapter 4. The algorithms used at the core routers and edge routers are discussed, along with formal mathematical notation of the 3-D switch.

Chapter 5 mainly focuses on hardware prototyping of the proposed 3-D Elevator Switch. This chapter extends the algorithms in Chapter 4 from theoretical design to practical hardware implementation. The chapter discusses the internal block diagram as well as the flow chart. It also elaborates the edge and core elevator module design in greater details. After discussing the components of every single component in 3-D optical

switching network, three sets of hardware experiments are conducted to verify the correctness of the system.

Chapter 6 summarizes the dissertation work. The application aware optical switching addresses the shortcoming OBS in terms of burst assembly and end-to-end latency. The 3-D elevator switching demonstrates its promising potential in solving the traffic blocking problem towards next generation optical networks. The prototyping effort of both application aware optical switching network testbed and 3-D optical switch provides valuable insights for practical adoption of new technologies.

# **Chapter 2 Background**

# 2.1 Overview of Dense Wavelength Division Multiplexing Technologies

Wavelength Division Multiplexing (WDM) multiplexes a number of optical signals onto a single optical fiber by using different frequency bands of laser light. The WDM system utilizes a multiplexer at the transmitting side and it decouples carrier signals using a de-multiplexer at the receiver end. It features an ultra-high bandwidth transmission without adding new optical fiber. A smooth and cost effective network upgrade is expected since there is no need for overhauling current optical backbone network infrastructure.

In reality, not all wavelengths are suitable for communication if attenuation characters and different types of dispersions are taken into consideration. The transmission distance is limited due to intermodal dispersion, chromatic dispersion, polarization mode dispersion as well as spreading of optical pulses. These limit the bandwidth of the fiber and traffic may not be able to distinguish at the receiver.

The wavelengths having the least effects are most favorable for transmission. These wavelengths are further standardized into six transmission bands. Each transmission band is called a transmission window. Table 1 shows the wavelength bands and their corresponding transmission window.

WDM technology is further categorized into two parts: coarse wavelength division multiplexing (CWDM) and dense wavelength division multiplexing (DWDM). CWDM provides up to 8 channels at the wavelength between 1530 nm to 1565 nm while

DWDM could brought closer to 80 channels with channel spacing of 50GHz in the same transmission window.

Table 1: wavelengths bands and corresponding transmission window

| The state of the s |                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | transmission window(nm)                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | , , , , , , , , , , , , , , , , , , , , |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1260-1360                               |  |

| O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1200-1300                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |

| E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1360-1460                               |  |

| L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1300-1400                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1460-1530                               |  |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1400-1330                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |

| С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1530-1565                               |  |

| C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1550-1505                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |

| L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1565-1625                               |  |

| L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1505-1025                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |

| II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1625-1675                               |  |

| O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1025-1075                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |

# 2.2 Optical Switching Network

### 2.2.1 Overview of Switching Networks

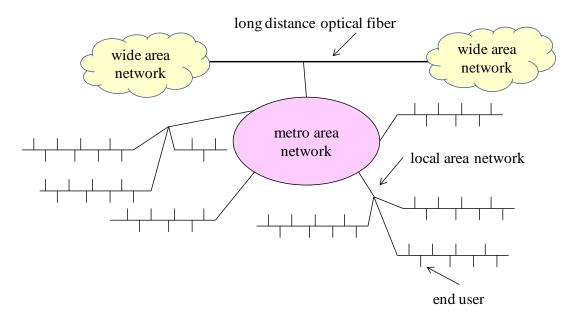

Optical switching networks have been commonly used with the increasing traffic originating from end users as well as high bandwidth applications. It could be found not only in wide area network (WAN), which is a long distance back bone network, but also in Metro area network (MAN) and local area network (LAN). Figure 1 is the network hierarchy of most common networks. WANs are connected through backbone long distance fibers. Incoming traffic from WAN is dropped onto MAN. MAN is a ring structure that connects all LANs together. Traffic from LANs will be added to MAN and be sent from MAN to WAN upon request.

Figure 1: current switching network hierarchy

When delivering the communications connectivity, the parts that actually reaches customers are traditional copper wire subscriber lines, Ethernet cables, coax cables and etc. This is typically the speed bottleneck in communication networks and usually refers to the last mile in order to emphasize the importance of the end users. To mitigate the problem of the last mile, fibers are gradually brought close to end users. Access networks are more and more utilizing optical and wireless media. Fiber network features high bandwidth but the mobility is limited. In contrast, wireless network is bandwidth limited but end users have more freedom of movement. Three switching technologies are discussed below.

#### 2.2.2 Electrical Packet Switching (EPS)