# OPTIMIZING THE PERFORMANCE OF DIRECTIVE-BASED PROGRAMMING MODEL FOR GPGPUS

\_\_\_\_\_

A Dissertation

Presented to

the Faculty of the Department of Computer Science

University of Houston

\_\_\_\_

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

By

Rengan Xu

May 2016

# OPTIMIZING THE PERFORMANCE OF DIRECTIVE-BASED PROGRAMMING MODEL FOR GPGPUS

Rengan Xu

APPROVED:

Dr. Barbara Chapman, Chairman

Dept. of Computer Science at University of Houston

Dr. Christoph F. Eick

Dept. of Computer Science at University of Houston

Dr. Shishir Shah

Dept. of Computer Science at University of Houston

Dr. Jaspal Subhlok

Dept. of Computer Science at University of Houston

Dr. Henri Calandra

TOTAL E&P Research and Technology USA

Dean, College of Natural Sciences and Mathematics

### Acknowledgements

I would like to sincerely express my gratitude to my advisor, Dr. Barbara Chapman, for providing me an excellent research group to learn and improve. It is a great honor to work in her group to perform cutting edge research. I am grateful for her encouragement and support which inspired me new research ideas and provided me with opportunities to attend top tier conferences and workshops and interact with other researchers in this community. I would also like to thank my committee members, Dr. Henri Calandra, Dr. Christoph F. Eick, Dr. Shishir Shah, and Dr. Jaspal Subhlok, who spent their precious time to review my dissertation and provide valued comments.

My mentor Sunita Chandrasekaran helped me a lot for several projects she was in charge of. It would be impossible for me to complete those projects without her guide and support. I am also very grateful to other fellow members in HPCTools group: Tony Curtis, Yonghong Yan, Deepak Eachempati, Dounia Khaldi, Abid Malik, and Xiaonan Tian for their valuable discussion and help.

I had opportunities to do my internship in both Repsol and TOTAL. I appreciate Mauricio Araya from Repsol, Henri Calandra and Maxime Hugues from TOTAL for giving me generous help during my internships.

Last but not least, I cannot express my appreciation for endless love and support from my girl friend, my brother and my parents. Thank you for accompanying me all the time.

This research work is supported in part by the Office of the Assistant Secretary of Defense for Research and Engineering (OASD(R&E)) under agreement number

FA8750-15-2-0119. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the Office of the Assistant Secretary of Defense for Research and Engineering (OASD(R&E)) or the U.S. Government.

# OPTIMIZING THE PERFORMANCE OF DIRECTIVE-BASED PROGRAMMING MODEL FOR GPGPUS

An Abstract of a Dissertation

Presented to

the Faculty of the Department of Computer Science

University of Houston

\_\_\_\_

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

\_\_\_\_

By

Rengan Xu

May 2016

#### Abstract

Accelerators have been deployed on most major HPC systems. They are considered to improve the performance of many applications. Accelerators such as GPUs have an immense potential in terms of high compute capacity but programming these devices is a challenge. OpenCL, CUDA and other vendor-specific models for accelerator programming definitely offer high performance, but these are low-level models that demand excellent programming skills; moreover, they are time consuming to write and debug. In order to simplify GPU programming, several directive-based programming models have been proposed, including HMPP, PGI accelerator model and OpenACC. OpenACC has now become established as the de facto standard. We evaluate and compare these models involving several scientific applications. To study the implementation challenges and the principles and techniques of directivebased models, we built an open source OpenACC compiler on top of a main stream compiler framework (OpenUH as a branch of Open64). In this dissertation, we present the required techniques to parallelize and optimize the applications ported with OpenACC programming model. We apply both user-level optimizations in the applications and compiler and runtime-driven optimizations. The compiler optimization focuses on the parallelization of reduction operations inside nested parallel loops. To fully utilize all GPU resources, we also extend the OpenACC model to support multiple GPUs in a single node. Our application porting experience also revealed the challenge of choosing good loop schedules. The default loop schedule chosen by the compiler may not produce the best performance, so the user has to manually try different loop schedules to improve the performance. To solve this issue, we developed a locality-aware auto-tuning framework which is based on the proposed memory access cost model to help the compiler choose optimal loop schedules and guide the user to choose appropriate loop schedules.

## Contents

| 1 | Introduction |        |                                                             | 1  |

|---|--------------|--------|-------------------------------------------------------------|----|

|   | 1.1          | Motiv  | ation                                                       | 1  |

|   | 1.2          | Contr  | ibutions and Dissertation Outline                           | 4  |

| 2 | Bac          | kgrou  | nd                                                          | 6  |

|   | 2.1          | Overv  | iew of GPU Architecture                                     | 7  |

|   | 2.2          | Overv  | iew of High-level Directive-based Programming Models        | 9  |

|   |              | 2.2.1  | Hybrid Multicore Parallel Programming workbench (HMPP) .    | 9  |

|   |              | 2.2.2  | PGI Accelerator Model                                       | 11 |

|   |              | 2.2.3  | OpenACC Programming Model                                   | 11 |

|   |              | 2.2.4  | OpenMP Programming Model                                    | 14 |

|   | 2.3          | Overv  | iew of Low-level Language-based Programming Models          | 15 |

|   |              | 2.3.1  | CUDA                                                        | 15 |

|   |              | 2.3.2  | OpenCL                                                      | 16 |

|   | 2.4          | Summ   | nary                                                        | 17 |

| 3 | Exp          | erime  | ntal Analysis of Porting Applications to GPU                | 18 |

|   | 3.1          | 2D-He  | eat Equation (Stencil domain)                               | 19 |

|   | 3.2          | Feldka | amp-Davis-Kress (FDK) Algorithm (Image Processing domain) . | 25 |

|   | 3.3          | CLEV   | ER Clustering (Data Mining domain)                          | 27 |

|   | 3.4       | Summ   | nary                                                    | 33      |

|---|-----------|--------|---------------------------------------------------------|---------|

| 4 | Par<br>Mo |        | ation and Optimization Strategies using Directive-based | l<br>34 |

|   | 4.1       | Strate | egies                                                   | 36      |

|   |           | 4.1.1  | Array Privatization                                     | 38      |

|   |           | 4.1.2  | Loop Scheduling Tuning                                  | 39      |

|   |           | 4.1.3  | Memory Coalescing Optimization                          | 40      |

|   |           | 4.1.4  | Data Motion Optimization                                | 41      |

|   |           | 4.1.5  | Cache Optimization                                      | 41      |

|   |           | 4.1.6  | Array Reduction Optimization                            | 42      |

|   |           | 4.1.7  | Scan Operation Optimization                             | 43      |

|   | 4.2       | Perfor | rmance Evaluation                                       | 44      |

|   | 4.3       | Discus | ssion                                                   | 51      |

|   |           | 4.3.1  | Programmability                                         | 51      |

|   |           | 4.3.2  | Performance Portability                                 | 51      |

| 5 | Cor       | npiler | and Runtime Driven Optimizations                        | 53      |

|   | 5.1       | Runti  | me                                                      | 54      |

|   |           | 5.1.1  | Runtime Library Components                              | 54      |

|   |           | 5.1.2  | Launch Configuration Setting                            | 57      |

|   |           | 5.1.3  | Execution Flow in Runtime                               | 57      |

|   | 5.2       | Reduc  | etion Algorithm                                         | 60      |

|   |           | 5.2.1  | Related Work                                            | 60      |

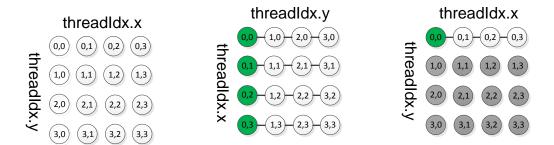

|   |           | 5.2.2  | Parallelism Mapping                                     | 62      |

|   |           | 5.2.3  | Parallelization of Reduction Operations for GPGPUs      | 64      |

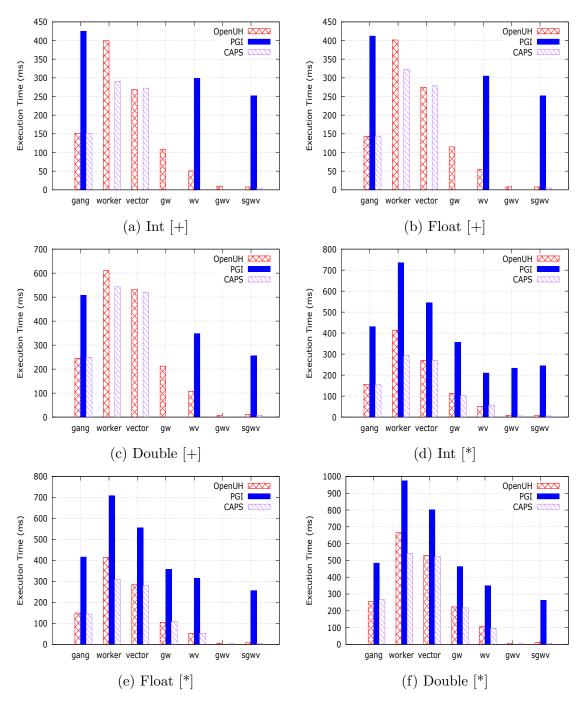

|   |           | 5.2.4  | Performance Evaluation                                  | 78      |

|   | 5.3       | Summ   | nory.                                                   | 25      |

| 6  | Opt   | timizations for Multiple GPUs                | 87    |

|----|-------|----------------------------------------------|-------|

|    | 6.1   | Related Work                                 | . 88  |

|    | 6.2   | Multi-GPU with OpenMP & OpenACC Hybrid Model | . 89  |

|    |       | 6.2.1 S3D Thermodynamics Kernel              | . 92  |

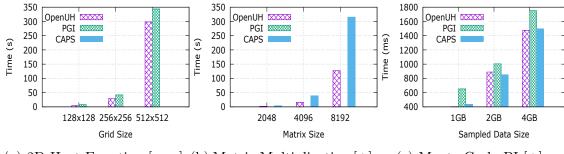

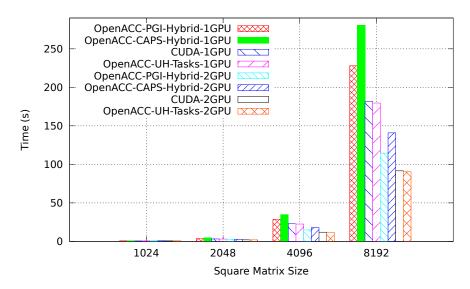

|    |       | 6.2.2 Matrix Multiplication                  | . 93  |

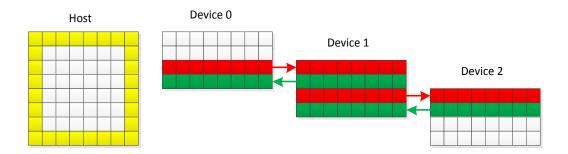

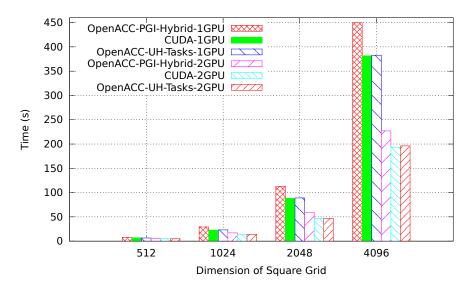

|    |       | 6.2.3 2D-Heat Equation                       | . 96  |

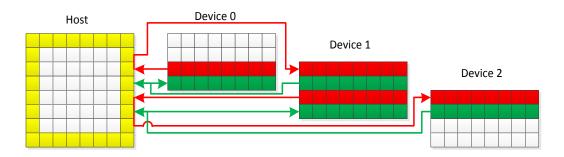

|    | 6.3   | Multi-GPU with OpenACC Extension             | . 102 |

|    |       | 6.3.1 Proposed Directive Extensions          | . 103 |

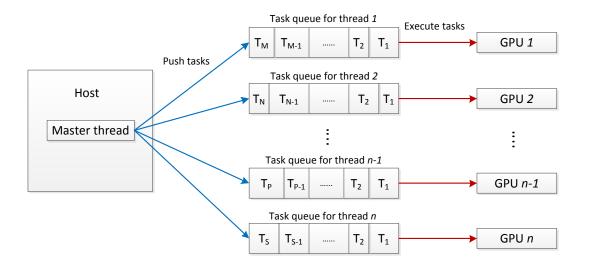

|    |       | 6.3.2 Task-based Implementation Strategy     | . 104 |

|    |       | 6.3.3 Evaluation with Benchmark Examples     | . 107 |

|    | 6.4   | Summary                                      | . 115 |

| 7  | Loc   | cality-Aware Auto-tuning for Loop Scheduling | 116   |

|    | 7.1   | Related Work                                 | . 117 |

|    | 7.2   | The Motivating Example                       | . 119 |

|    | 7.3   | Loop Scheduling Auto-tuning                  | . 121 |

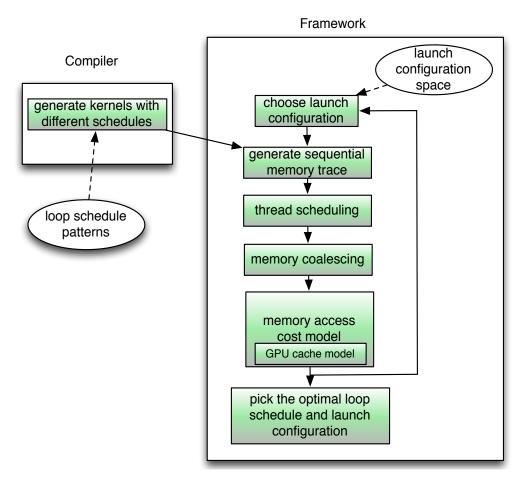

|    |       | 7.3.1 The Auto-tuning Framework              | . 121 |

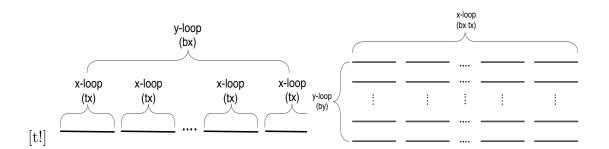

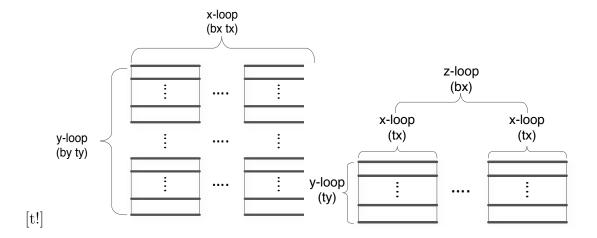

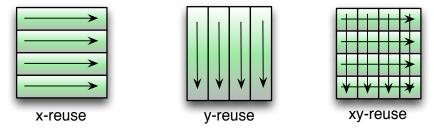

|    |       | 7.3.2 Loop Schedule Patterns                 | . 123 |

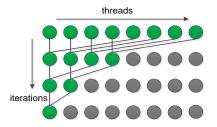

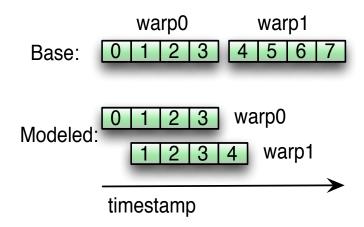

|    |       | 7.3.3 Thread Scheduling                      | . 127 |

|    |       | 7.3.4 Memory Access Cost Model               | . 129 |

|    | 7.4   | Performance Evaluation                       | . 134 |

|    |       | 7.4.1 Benchmarks                             | . 135 |

|    |       | 7.4.2 Supprt Vector Machine (SVM)            | . 140 |

|    | 7.5   | Summary                                      | . 143 |

| 8  | Cor   | nclusions and Future Work                    | 145   |

| D; | iblio | graphy                                       | 148   |

# List of Figures

| 2.1 | Nvidia Kepler GPU architecture                     | 7  |

|-----|----------------------------------------------------|----|

| 2.2 | GPU threads hierarchy                              | 7  |

| 3.1 | HMPP implementation of 2D-Heat Equation            | 22 |

| 3.2 | OpenACC implementation of 2D-Heat Equation         | 23 |

| 3.3 | Application speedup with different models          | 24 |

| 4.1 | Array privatization example                        | 38 |

| 4.2 | Loop scheduling example                            | 40 |

| 4.3 | Solutions of array reduction in EP benchmark       | 43 |

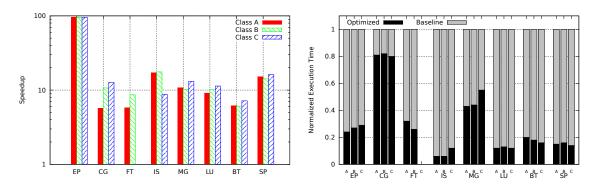

| 4.4 | NPB-ACC speedup over NPB-SER                       | 46 |

| 4.5 | NPB-ACC performance improvement after optimization | 46 |

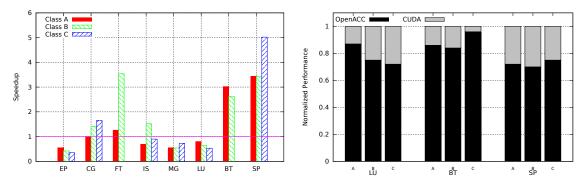

| 4.6 | NPB-ACC speedup over NPB-OCL                       | 48 |

| 4.7 | NPB-ACC performance comparison with NPB-CUDA       | 48 |

| 5.1 | Runtime region stack structure                     | 56 |

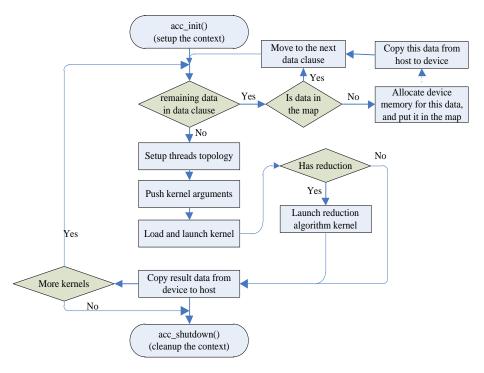

| 5.2 | Execution flow with OpenACC runtime library        | 58 |

| 5.3 | OpenACC execution flow example                     | 59 |

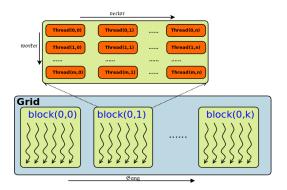

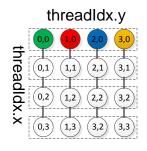

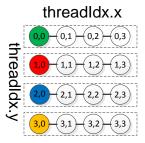

| 5.4 | GPGPU thread block hierarchy                       | 62 |

| 5.5 | Loop nest example with OpenACC parallelisms        | 63 |

| 5.6 | Reduction in vector                                | 66 |

| 5.7  | Reduction in worker                                                           | 67  |

|------|-------------------------------------------------------------------------------|-----|

| 5.8  | Reduction in gang                                                             | 67  |

| 5.9  | Parallelization comparison for vector reduction                               | 68  |

| 5.10 | Interleaved log-step reduction                                                | 69  |

| 5.11 | Parallelization comparison for worker reduction                               | 70  |

| 5.12 | Example of RMP in different loops                                             | 73  |

| 5.13 | Example of RMP in the same loop                                               | 75  |

| 5.14 | Performance comparison of OpenACC compilers using reduction test suite        | 81  |

| 5.15 | Performance comparison for three applications                                 | 82  |

| 5.16 | Code snippet for three applications                                           | 82  |

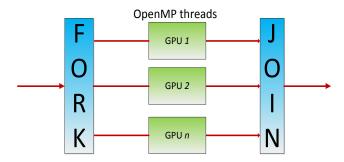

| 6.1  | A multi-GPU solution using the hybrid OpenMP & OpenACC model                  | 91  |

| 6.2  | S3D thermodynamics kernel in single GPU                                       | 92  |

| 6.3  | S3D thermodynamics kernel in multi-GPU using hybrid model                     | 94  |

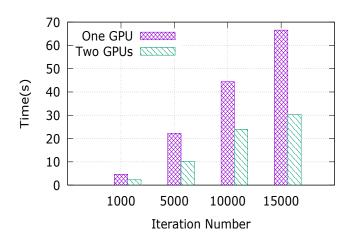

| 6.4  | Performance comparison of S3D                                                 | 95  |

| 6.5  | A multi-GPU implementation of MM using hybrid model                           | 96  |

| 6.6  | Performance comparison using hybrid model                                     | 97  |

| 6.7  | Single GPU implementation of 2D-Heat Equation                                 | 99  |

| 6.8  | Multi-GPU implementation with hybrid model - 2D-Heat Equation $$ .            | 100 |

| 6.9  | Multi-GPU implementation strategy for 2D-Heat Equation using the hybrid model | 101 |

| 6.10 | Task-based multi-GPU implementation in OpenACC                                | 106 |

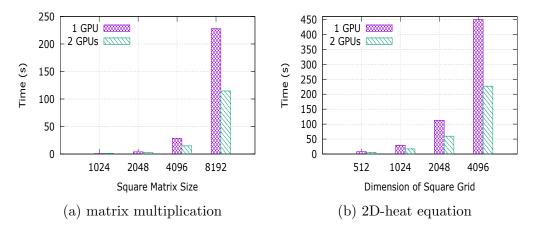

| 6.11 | A multi-GPU implementation of MM using OpenACC extension                      | 110 |

| 6.12 | Performance comparison for MM using multiple models                           | 112 |

| 6.13 | Multi-GPU implementation with OpenACC extension - 2D-Heat Equation            | 113 |

| 6.14 | Multi-GPU implementation of 2D-Heat Equation using OpenACC extension          | 114 |

|------|-------------------------------------------------------------------------------|-----|

| 6.15 | Performance comparison for 2D-Heat Equation using multiple models             | 114 |

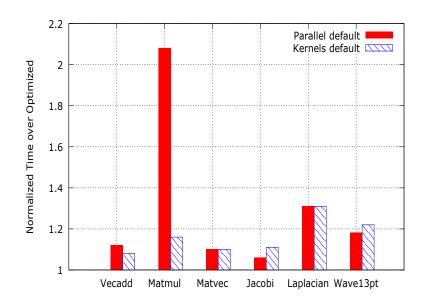

| 7.1  | Loop scheduling comparison                                                    | 120 |

| 7.2  | The framework of auto-tuning for loop scheduling                              | 121 |

| 7.3  | Loop schedule $2_{-1}$                                                        | 126 |

| 7.4  | Loop schedule 2_2                                                             | 126 |

| 7.5  | Loop schedule 2_3                                                             | 126 |

| 7.6  | Loop schedule $3_{-}1$                                                        | 126 |

| 7.7  | Thread scheduling used in the auto-tuning framework                           | 128 |

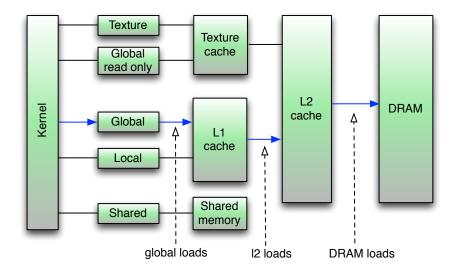

| 7.8  | GPU memory hierarchy                                                          | 131 |

| 7.9  | L1 cache modeling                                                             | 132 |

| 7.10 | Data reuse patterns                                                           | 135 |

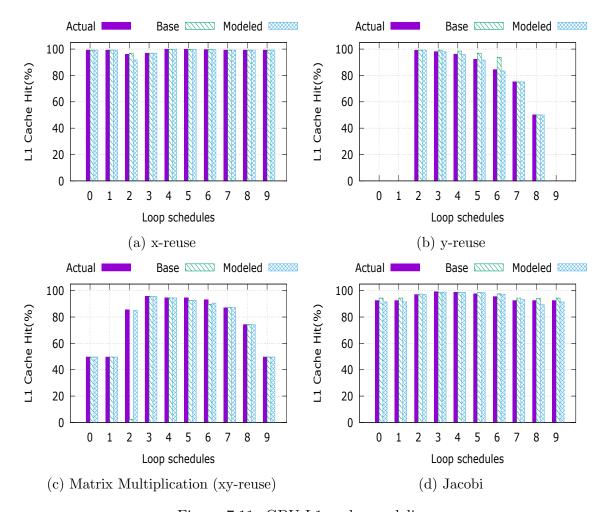

| 7.11 | GPU L1 cache modeling                                                         | 137 |

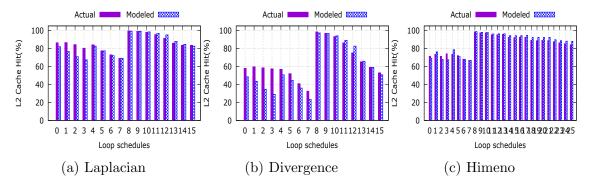

| 7.12 | GPU L2 cache modeling                                                         | 138 |

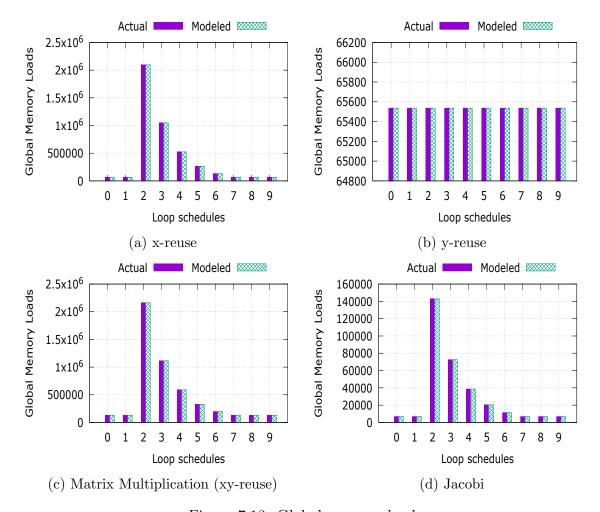

| 7.13 | Global memory loads                                                           | 139 |

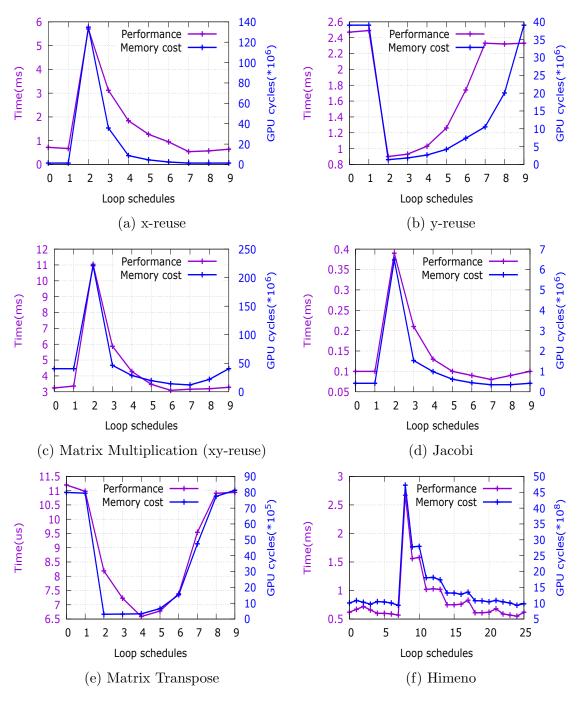

| 7.14 | Plots demonstrating correlation of Performance vs Memory Access Cost Modeling | 141 |

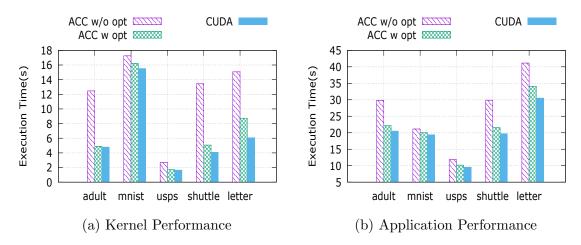

| 7.15 | Performance of ACC-SVM against CUDA-SVM                                       | 142 |

# List of Tables

| 2.1 | Major features comparison among different models                                                                        | 9   |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Specification of experiment machine                                                                                     | 19  |

| 3.2 | L10Ovals dataset characteristics                                                                                        | 31  |

| 3.3 | Earthquake dataset characteristics                                                                                      | 31  |

| 3.4 | Time(in sec) consumed by Serial, CUDA, HMPP, PGI and OpenACC versions of the code, only for most time-consuming dataset | 33  |

| 4.1 | Comparing elapsed time for NPB-ACC, NPB-SER, NPB-OCL, and NPB-CUDA                                                      | 45  |

| 5.1 | CUDA terminology in OpenACC implementation                                                                              | 64  |

| 5.2 | Performance results of OpenACC compilers using reduction test suite                                                     | 80  |

| 7.1 | Loop scheduling in different cases                                                                                      | 120 |

| 7.2 | Reuse distance example                                                                                                  | 133 |

| 7.3 | Evaluation results                                                                                                      | 140 |

| 7.4 | Characteristics of the experiment dataset                                                                               | 142 |

## Chapter 1

### Introduction

#### 1.1 Motivation

Recent years have seen a rise of massively-parallel supercomputing systems that are based on heterogeneous architectures combining multi-core CPUs with General-Purpose Graphic Processing Units (GPGPUs). While such systems offer a promising performance with reasonable power consumption, programming accelerators in an efficient manner is still a challenge. The existing low-level APIs such as CUDA and OpenCL usually require users to be expert programmers and restructure the code largely. Optimized kernels are written that are usually coupled with specific devices. This leads to a less productive and more error prone software development process that is challenging to be adopted by the rapidly growing HPC market.

Recent approaches for programming accelerators include directive-based, high-level programming models for accelerators. It allows the users to insert non-executable pragmas and guide the compiler to handle low-level complexities of the system. The major advantage of the directive-based approach is that it offers a high-level programming abstraction thus simplifying the code maintenance and improving productivity.

As different directive-based programming models offer different feature sets, the code portability therefore becomes a major issue. As a joint standardization between CAPS, CRAY, PGI and NVIDIA, OpenACC was first released in November 2011, which aims to provide a directive-based portable programming model for accelerators. By using OpenACC, it allows the users to maintain a single code base that is compatible with various compilers, while on the other hand, the code is also portable across different possible types of platforms.

Our first attempt is to study the feasibility and applicability of these directive-based models when they are applied to scientific applications consisting of varied characteristics. These models allow programming without the need to explicitly manage the data transfer between CPU and GPU, device start-up and shut-down to name a few. We will explore three directive-based programming models, HMPP, PGI, and OpenACC and assess the models using scientific applications. We compare and contrast the performance achieved by these directives to that of the corresponding hand-written CUDA version of the application. Besides these mainstream directive-based models, there are some other research-based directive-based models including hiCUDA [35], CUDA-lite [66], Mint [67], and OpenMPC [48], but the compiler implementation for these models are not mature enough for evaluation.

Since OpenACC is a high-level directive-based model, the implementations of this model usually translates it to a low-level model such as CUDA or OpenCL. The low-level models like CUDA or OpenCL are language-based model, therefore it is flexible for the user to apply any optimization they want. But this requires the user to throughly understand the underlying architecture so that the applied optimizations can utilize the architecture efficiently. The high-level model OpenACC is directive-based, therefore it requires the compiler to apply those optimizations automatically. However, without enough information, the compiler is not able to do the optimizations as well as the user who is an expert in both the ported application and the architecture. Even though the compiler can apply some optimizations automatically, it may not achieve the expected speedup as the compiler does not have a full view of the whole application. Because of these reasons, the application ported with OpenACC and CUDA usually have a performance gap. The goal of our work is to apply both manual and automatic optimizations to optimize the performance of OpenACC programs.

To understand OpenACC model throughly, we start to use it to port large applications. We chose the NAS Parallel Benchmarks (NPB) which is a well recognized benchmark suite for evaluating current and emerging multi-core/many-core hardware architectures. We present a set of optimization techniques to tune the application performance. Besides those optimization techniques applied in the application level, we also present the optimizations in compiler and runtime level. The optimizations we focus on include the runtime library, reduction algorithm and multi-GPU. Finally, we focus on the loop scheduling auto-tuning optimization which aims to find

the optimal mapping from a nested loop to the GPU threads hierarchy.

#### 1.2 Contributions and Dissertation Outline

In summary, to make the directive-based programming model for GPUs more mature and broaden its impact in both academia and industry, several research issues are addressed in this dissertation. Chapter 2 provides the background of the research work in this dissertation. The contributions of this dissertation are as follows:

- In Chapter 3, we compare the features of different high-level directive-based programming models for GPUs and the performance of applications using these models.

- In Chapter 4, to understand the root cause of the performance of directive-based model, we use NAS Parallel Benchmark (NPB) suite as example and present a set of optimizations to tune the application performance. Most of these optimizations are applied manually in the application level. We analyze a number of choices and combinations of optimization techniques and study their impact on application performance. We learn that poorly selected options or using system default options for optimizations may lead to significant performance degradation. We also compare the performance of OpenACC NPB with that of the well-tuned OpenCL and CUDA versions of the benchmarks to present the reasoning behind the performance gap.

- In Chapter 5, we present the optimizations applied automatically in the compiler and runtime for OpenACC applications. We demonstrate how the runtime tracks and manages all the data correctly and efficiently. We also propose and demonstrate new compiler algorithms to parallelize the comprehensive reduction operations within three levels of parallelism. Our implementation covers all possible reduction cases, reduction types and operand data types.

- In Chapter 6, we enable multi-GPU programming on single node by using two approaches. First we explore and evaluate the OpenMP & OpenACC hybrid model. Second, based on the disadvantages of the hybrid model approach, we propose a set of new directives to extend the OpenACC model to support multiple GPUs.

- In Chapter 7, we present a locality-aware auto-tuning framework for loop scheduling that uses an analytical model to find the optimal loop schedule which maps a nested loop to the GPU threads hierarchy. The framework extends the reuse distance model for GPU cache modeling.

In this dissertation, the related work is not in a separate chapter, it is discussed in each chapter. Chapter 8 concludes this dissertation.

### Chapter 2

## Background

In this chapter, we give the background of our research work. First, we give the overview of the GPU architecture which is the platform our research based on. Second, we give an overview of the directive-based programming models for GPUs, including Hybrid Multicore Parallel Programming workbench (HMPP) [1], PGI accelerator model [30] and OpenACC [10] which is the standard of high-level directive-based programming model for accelerators. Third, since we use OpenMP & OpenACC hybrid model in the multi-GPU research work, we also discuss the OpenMP programming model which is the de facto standard of shared-memory system programming.

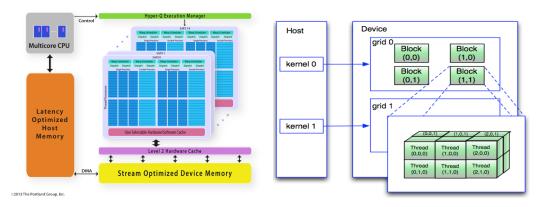

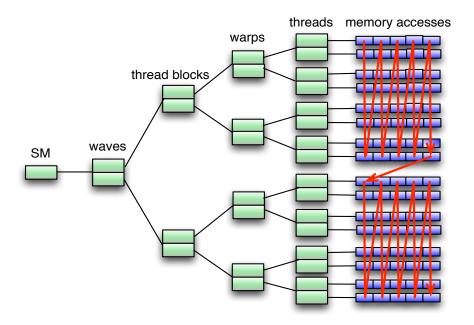

Figure 2.1: Nvidia Kepler GPU archi- Figure 2.2: GPU threads hierarchy tecture<sup>1</sup>

#### 2.1 Overview of GPU Architecture

GPU architectures differ significantly from that of traditional processors. We illustrate this using Nvidia Kepler GPU which is shown in Figure 2.1. Employing a Single Instruction Multiple Threads (SIMT) architecture, NVIDIA GPUs have hundreds of cores that can process thousands of software threads simultaneously. GPUs organize both hardware cores and software threads into two-level of parallelism. Hardware cores are organized into an array of Streaming Multiprocessors (SMs), each SM consisting of a number of cores named as Scalar Processors (SPs). An execution of a computational kernel, e.g. CUDA kernel, will launch a (software) thread grid. As shown in Figure 2.2, a grid consists of multiple thread blocks whose shape could be 1D, 2D, or 3D. And each thread block consists of multiple threads whose shape could also be 1D, 2D, or 3D. The GPU is connected to the CPU by a PCI-E bus. We also refer **host** to CPU and **device** to GPU. Since the host and the device are

<sup>&</sup>lt;sup>1</sup>https://www.pgroup.com/lit/articles/insider/v2n1a5.htm

separate, in the GPU execution model, the CPU needs to first move the input data from CPU to GPU, then perform the computation within GPU, finally move the output result back to CPU. When CPU moves data to GPU, it can only move to the GPU DRAM as it is the only memory that can communicate with CPU. DRAM is the largest (usually GB) but also the slowest memory in GPU. Like CPU, GPU also has caches. Each SM has its own L1 cache (e.g. 16KB) and shared memory (e.g. 48KB) which are only accessible for the threads in this SM. All SMs share a unified L2 cache (e.g. 1.5MB). The shared memory is a user programmable cache while L1 and L2 are cached automatically by the GPU system. Each GPU thread has its own registers.

For programmers, the challenges to efficiently utilize the massive parallel capabilities of GPUs are to map the algorithms onto thread hierarchy, and to lay out data on both the global memory and shared memory to maximize coalesced memory access for the threads. Using low-level programming models such as CUDA and OpenCL to do this has been known as not only time consuming but also the software created are not identical to its original algorithms significantly decreasing code readability.

Table 2.1: Major features comparison among different models

| Features    |                       | OpenACC                      | HMPP                                             | PGI                          |

|-------------|-----------------------|------------------------------|--------------------------------------------------|------------------------------|

|             | memory<br>allocation  | acc_malloc                   | allocate                                         | acc_malloc                   |

| Data        | memory free           | acc_free                     | release                                          | acc_free                     |

|             | data<br>movement      | copyin<br>copyout<br>copy    | args[*].io=<br>in,out,inout                      | copyin<br>copyout<br>copy    |

|             | synchronization       | update device<br>update host | advancedload<br>delegatedstore                   | update device<br>update host |

| Computation | kernels<br>offloading | parallel<br>kernels          | codelet&callsite                                 | region                       |

| Computation | loop<br>scheduling    | gang<br>worker<br>vector     | gridify                                          | parallel<br>vector           |

|             | loop<br>optimization  | collapse<br>tile<br>auto     | permute<br>distribute<br>fuse,unroll<br>jam,tile | unroll                       |

# 2.2 Overview of High-level Directive-based Programming Models

In this section, we provide details about three directive-based models that are being evaluated in this dissertation. The major features among these models are summarized in Table 2.1.

# 2.2.1 Hybrid Multicore Parallel Programming workbench (HMPP)

HMPP is a directive-based programming model used to build parallel applications running on manycore systems. It is a source-to-source compiler that can translate directive-associated functions or code portions into CUDA or OpenCL kernels.

In HMPP, the two most important concepts are "codelet" and "callsite" [1]. The "codelet" concept represents the function that will be offloaded to the accelerator, and "callsite" is the place to call the "codelet". It is the programmer's responsibility to annotate the code by identifying the codelets and inform the compiler about the codelets and where to call the same. In the steps of compilation, the annotated code is parsed by the HMPP preprocessor to extract the codelets and to translate the directives into runtime calls. The preprocessed code is then compiled and linked to HMPP runtime with a general-purpose host compiler. If the accelerator is not found or not available, the program execution can fall back to the original sequential version. HMPP also supports the "region" directive which only offloads part of a function into the accelerator and the "region" is a merge of codelet/callsite directives. The main issue with programming accelerators is the data transfer between the accelerator and the host. HMPP offers many data transfer policies as part of the optimization strategies. The user can manually control the data transfer, i.e. transfer the data every time the codelet is called or transfer the data only during the first time when the codelet is called. It can also be automatically decided by the compiler.

HMPP also provides a set of directives to improve the performance by enhancing the code generation. In the codelet, the user can put the read-only data into constant memory, preload the frequently-used data into shared memory, or explicitly specify the grid size in NVIDIA architecture. If the loop is so complex that the compiler is not able to parse, the user can give some hints to the compiler that all iterations in the loop are independent.

#### 2.2.2 PGI Accelerator Model

PGI accelerator programming model contains a set of directives, runtime-library routines and environment variables [30]. The directives include data directives, compute directives and loop directives. The compute directive specifies a portion of the program to be offloaded to the accelerator. There is an implicit data region surrounding the compute region, which means data will be transferred from the host to the accelerator before the compute region and be transferred back from the accelerator to the host at the exit of compute region. Data directives allow the programmer to manually control where to transfer the data other than the boundaries of compute region. The loop directives enable the programmer to control how to map loop parallelism in a fine-grained manner. The user can add these directives incrementally so that the original code structure is preserved. The compiler maps loop parallelism onto the hardware parallelism using the planner [71]. PGI optimizes the data transfer by "data region" directive and its clauses and be able to remove unnecessary data copies. Using the loop scheduling directive, the user can add the data in the highest level of the data cache by using "cache" clause and this helps in improving the data-access speed.

#### 2.2.3 OpenACC Programming Model

OpenACC is an emerging GPU-based programming model that is working towards establishing a standard in directive-based accelerator programming. As a joint standardization between CAPS, CRAY, PGI, and NVIDIA, OpenACC was first released

in November 2011, which aims to provide a directive-based portable programming model for accelerators. By using OpenACC, it allows the users to maintain a single code base that is compatible with various compilers, while on the other hand, the code is also portable across different possible types of platforms.

OpenACC is based on the use of pragmas or directives that allow the application developers to mark regions of code for acceleration in a vendor-neutral manner. It builds on top of prior efforts by several vendors (notably PGI and CAPS Enterprise) to provide parallel-programming interface for heterogeneous systems, with a particular emphasis on platforms that are comprised of multicore processors as well as GPUs. Among others, OpenACC is intended for use on the nodes of large-scale platforms such as the Titan system at ORNL, where CPUs and NVIDIA GPUs are used in concert to solve some of the nations most urgent scientific problems.

The OpenACC model is based on the PGI model, hence the former inherits most of the concepts from the latter. However some of the differences are: unlike PGI's single "region" compute directive, OpenACC offers two types of compute directives "parallel" and "kernels". The directive "kernels" is similar to PGI's "region" that surrounds the loops to execute on the accelerator device. With the "parallel" directive, however, if there is any loop inside the following code block and the user does not specify any loop scheduling technique, all the threads will execute the full loop. OpenACC supports three levels parallelism: gang, worker and vector, while PGI only defines two levels of parallelism: parallel and vector. Both OpenACC and PGI models allow the compute region to use the "async" clause to execute asynchronously with the host computation and the user can synchronize these asynchronous activities

with the "wait" directive. They also have a similar set of runtime library routines, including getting the total number of accelerators available, getting & setting the device type and number, checking & synchronizing the asynchronous activities and starting up & shutting down the accelerator. Unlike PGI, OpenACC can allocate and free a part of accelerator memory using  $acc_malloc()$  and  $acc_free()$  functions.

The OpenACC feature set includes pragmas, or directives, that can be used in conjunction with C, C++, and Fortran code to program accelerator boards. OpenACC can work with OpenMP to provide a portable programming interface that addresses the parallelism in a shared memory multicore system as well as accelerators. A key element of the interface is the parallel construct that launches gangs that will execute in parallel. Each of the gangs may support multiple workers that execute vector or SIMD constructs. A variety of clauses are provided that enables conditional execution, controls the number of threads, specifies the scope of the data accessed in the accelerator parallel region, and determines if the host CPU should wait for the region to complete before proceeding with other work.

Suitable placement of data and careful management of required data transfer between host and accelerator is critical for application performance on the emerging heterogeneous platforms. Accordingly, there are a variety of features in OpenACC that enables the application developer to allocate data and determine whether data needs to be transferred between the configured devices. The features also enable control this transfer, including the values to be updated on the host/accelerator by copying current data values on the accelerator/host, respectively. These features are complemented by a set of library routines to obtain device information or set device

types, test for completion of asynchronous activities, as well as a few environment variables to identify the devices that will be used.

OpenACC standard gives great flexibility to the compiler implementation. For instance, different compilers can have different interpretation of OpenACC three level parallelisms: coarse grain parallelism "gang", fine grain parallelism "worker", and vector parallelism "vector". On an NVIDIA GPU, PGI maps each gang to a thread block, and vector to threads in a block and it just ignores worker; CAPS maps gang to the x-dimension of a grid block, worker to the y-dimension of a thread block, and vector to the x-dimension of a thread block; Cray maps each gang to a thread block, worker to warp, and vector to SIMT group of threads.

#### 2.2.4 OpenMP Programming Model

OpenMP is a high-level directive-based programming model for shared memory multi-core platforms. The model consists of a set of directives, runtime library routines, and environment variables. The user just needs to simply insert the directives into the existing sequential code, with minor changes or no changes to the code. OpenMP adopts the fork-join model. The model begins with an initial main thread, then a team of threads will be forked when the program encounters a parallel construct, and all other threads will join the main thread at the end of the parallel construct. In the parallel region, each thread has its own private variables and does the work on its own piece of data. The communication between different

threads is performed via shared variables. In the case of a data race condition, different threads will update the shared variable atomically. Starting from 3.0, OpenMP introduced *task* concept [17] that can effectively express and solve the irregular parallelism problems such as unbounded loops and recursive algorithms. To make the task implementation efficient, the runtime needs to consider the task creation, task scheduling, task switching, and task synchronization, etc. OpenMP 4.0 released in 2013 includes support for accelerators.

# 2.3 Overview of Low-level Language-based Programming Models

#### 2.3.1 CUDA

CUDA, which stands for Compute Unified Device Architecture, is a parallel computing platform and a language-based programming model specific for NVIDIA GPUs. A CUDA program is a unified source code including both host and device code. The host code is pure ANSI C code and the device code is the extension of ANSI C which provides some keyword for labeling data parallel functions called *kernels*. The host code and device code are compiled separately. The host code is compiled by the host's standard C compiler and the device code is compiled by Nvidia compiler nvcc. The host code is executed on the host and offloads the device code to be executed on the device. CUDA provides both a low level driver API and a high level runtime API. The programmer can use these APIs to manage the execution context environment,

the device memory allocation and deallocation, the data movement between CPU and GPU, the asynchronous data movement and kernel execution, etc. Since CUDA is proprietary to NVIDIA, hence the performance of CUDA program is optimized for NVIDIA GPU, but the disadvantage is that the same program cannot be migrated to other vendor's GPUs which has less portability.

#### 2.3.2 OpenCL

OpenCL, which stands for Open Computing Language, is a language-based programming model for heterogeneous platforms including CPUs, GPUs, digital-signal processors (DSPs) and field-programmable gate arrays (FPGAs), etc. OpenCL is an extension of ISO C99 and provides an API to control the platform and program execution on the compute devices. Since OpenCL is an open standard, the benefit of OpenCL is cross-vendor and cross-platform software portability. Unlike CUDA model that has only one implementation in NVIDIA, OpenCL has implementations in multiple vendors such as AMD, Apple, IBM, Intel, Nvidia, Qualcomm, and Samsung.

#### 2.4 Summary

In this chapter, we give an overview of the GPU architecture and both the high-level directive-based programming models and low-level language-based programming models for GPUs. The high-level models are able to simplify the GPU programming but at the cost of performance loss because it is not as flexible as the low-level models. The low-level models allow the users to take advantage of the hardware features by communicating to the driver and runtime directly. Therefore they are more flexible for the users and provide more opportunities to manually tune applications, but at the cost of steep learning curve and time-consuming development. The following chapters try to evaluate the performance gap between the directive-based model OpenACC and the low-level model CUDA and apply optimizations within OpenACC to decrease the performance gap. Some research issue like the loop scheduling tuning that exists in both OpenACC and CUDA will also be addressed.

### Chapter 3

# Experimental Analysis of Porting Applications to GPU

In this chapter, we assess and evaluate three directive-based programming models, HMPP, PGI, and OpenACC with respect to their run-time performance, program complexity, and ease of use. We compare the performance obtained of the three programming models with that of the native CUDA and the sequential version. The OpenACC model is very attractive as it standardizes programming. To the best of our knowledge, this is one of the very few work that systematically evaluates the models. This work is one of the first to compare OpenACC with other programming models. We have explored two vendor compilers supporting the OpenACC model. To maintain confidentiality we will be referring to the 2 vendor compilers in this chapter as OpenACC\_Compiler\_A and OpenACC\_Compiler\_B.

In this section, we evaluate three directive-based programming models using three

scientific applications. The experimental platform is a server machine that is a multicore system consisting of two NVIDIA C2075 GPUs. Configuration details are shown in Table 3.1. We use the most recent versions for all the compilers being discussed in this chapter. We use GCC 4.4.7 for all the sequential versions of the programs as well as for the HMPP host compiler. We use -O3 as the compilation flag for optimization purposes. As part of the evaluation process, we highlight several features of the programming models, that is best suited for the characteristics of an application. We compare the performances achieved by each of the models with that of the sequential and CUDA versions of the code. We consider wall-clock time as the evaluation measurement.

Table 3.1: Specification of experiment machine

| Item               | Description       |

|--------------------|-------------------|

| Architecture       | Intel Xeon x86_64 |

| CPU socket         | 2                 |

| Core(s) per socket | 8                 |

| CPU frequency      | 2.27GHz           |

| Main memory        | 32GB              |

| GPU Model          | Tesla C2075       |

| GPU cores          | 448               |

| GPU clock rate     | 1.15GHz           |

| GPU global memory  | 5375MB            |

#### 3.1 2D-Heat Equation (Stencil domain)

The formula to represent 2D-heat equation is explained in [59] and is given as follows:

$$\frac{\partial T}{\partial t} = \alpha \left( \frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial y^2} \right)$$

where T is temperature, t is time,  $\alpha$  is the thermal diffusivity, and x and y are points in a grid. To solve this problem, one possible finite difference approximation is:

$$\frac{\Delta T}{\Delta t} = \alpha \left[ \frac{T_{i+1,j} - 2T_{i,j} + T_{i-1,j}}{\Delta x^2} + \frac{T_{i,j+1} - 2T_{i,j} + T_{i,j-1}}{\Delta y^2} \right]$$

where  $\Delta T$  is the temperature change over time  $\Delta t$  and i, j are indices in a grid. At the beginning, there is a grid that has boundary points with initial temperature and the inner points that need to update their temperature. Then each inner point updates its temperature by using the previous temperature of its neighboring points and itself. The temperature updating operation for all inner points in a grid needs to last long enough which means many iterations is required to get the final stable temperatures. In our program, the number of iterations is 20000, and we increase the grid size gradually from 128\*128 to 4096\*4096. Figure 3.1 contains the code for temperature updating kernel and the steps to call this kernel in the main program.

It is possible to parallelize the 2D heat equation using the most basic directives from OpenACC, HMPP, and PGI. For example, we use the OpenACC model and insert "#pragma acc kernels loop independent" before the nested loop inside the temperature updating kernel. The main point to note with this algorithm is performance. By profiling the basic implementation, we found that the data is transferred back and forth in every main iteration step. The cost of data transfer is so expensive that the parallelized code is even slower than the original native version. The challenging task is executing the pointer-swapping operation. In iteration i, temp1 is the input and temp2 stores the output data. Before proceeding to iteration i + 1, these two pointers are swapped so that temp1 holds the output data in iteration i while temp2 will wait to store the output data in iteration i + 1. An intermediate pointer temp

is needed to swap these two pointers. Since *temp* resides on the host while *temp1* and *temp2* reside on the accelerator, they cannot be swapped directly. The key is how to swap these pointers inside the accelerator internally so that unnecessary data transfer is removed.

While using the OpenACC model, we use the deviceptr data clause to specify temp as a device pointer, i.e, the pointer will always remain on the accelerator side. To avoid transferring the data during each step, data directive needs to be added so that the data is transferred only before and after the main loops. After all the iterations are completed we need to transfer data in temp1 instead of temp2 from GPU to CPU since the pointers of temp1 and temp2 have been swapped earlier. Inside the temperature-updating kernel, the nested loop is collapsed because every iteration is independent. Using HMPP, we have considered copying the input and output data just once by setting the data transfer policy of temp\_in and temp\_out to manual. To ensure that the correct data is being accessed, we used HMPP's data mirroring directive so that we refer to arguments temp1 and temp2 with their host addresses. Data mirroring requires data mirrors to be declared and allocated before being used. HMPP could collapse the nested loop in the kernel by using "gridify(j,i)" code generation directive. Figure 3.1 and Figure 3.2 show the code snippet using both HMPP and OpenACC model.

Note that this application is sensitive to floating-point operations. We found that the precision of the floating-point values of the final output temperature on the GPU is different to the values on the CPU. This is due to Fused Multiply-Add (FMA) [70], here the computation  $\operatorname{rn}(X * Y + Z)$  occurs in a single step and rounded

```

\mbox{\tt\#pragma} hmpp heat codelet, target=CUDA &

#pragma hmpp & , args[temp_in].io=in &

#pragma hmpp & , args[temp_out].io=inout &

#pragma hmpp & , args[temp_in,temp_out].mirror &

#pragma hmpp & , args[temp_in, temp_out].transfer=manual

void step_kernel(int ni, int nj, float tfac,

float *temp_in, float *temp_out) {

// loop over all points in domain (except boundary)

#pragma hmppcg gridify(j,i)

for (j=1; j < nj-1; j++) {

for (i=1; i < ni-1; i++) {

// find indices into linear memory

// for central point and neighbours

i00 = I2D(ni, i, j);

im10 = I2D(ni, i-1, j);

ip10 = I2D(ni, i+1, j);

iOm1 = I2D(ni, i, j-1);

i0p1 = I2D(ni, i, j+1);

// evaluate derivatives

d2tdx2 = temp_in[im10]-2*temp_in[i00]+temp_in[ip10];

d2tdy2 = temp_in[i0m1]-2*temp_in[i00]+temp_in[i0p1];

// update temperatures

temp_out[i00] = temp_in[i00]+tfac*(d2tdx2 + d2tdy2);

}

#pragma hmpp heat allocate, data["temp1"], size={ni*nj}

#pragma hmpp heat advancedload, data["temp1"]

#pragma hmpp heat allocate, data["temp2"], size={ni*nj}

#pragma hmpp heat advancedload, data["temp2"]

// main iteration loop

for (istep=0; istep < nstep; istep++) {</pre>

#pragma hmpp heat callsite

step_kernel(ni, nj, tfac, temp1, temp2);

// swap the temp pointers

temp = temp1;

temp1 = temp2;

temp2 = temp;

#pragma hmpp heat delegatedstore, data[temp1]

#pragma hmpp heat release

```

Figure 3.1: HMPP implementation of 2D-Heat Equation

```

void step_kernel(...)

#pragma acc kernels present(temp_in[0:ni*nj], temp_out[0:ni*nj])

// loop over all points in domain (except boundary)

#pragma acc loop collapse(2) independent

for (j=1; j < nj-1; j++) {

for (i=1; i < ni-1; i++) {

// find indices into linear memory

// for central point and neighbours

i00 = I2D(ni, i, j);

im10 = I2D(ni, i-1, j);

ip10 = I2D(ni, i+1, j);

i0m1 = I2D(ni, i, j-1);

i0p1 = I2D(ni, i, j+1);

// evaluate derivatives

d2tdx2 = temp_in[im10]-2*temp_in[i00]+temp_in[ip10];

d2tdy2 = temp_in[i0m1]-2*temp_in[i00]+temp_in[i0p1];

// update temperatures

temp_out[i00] = temp_in[i00]+tfac*(d2tdx2 + d2tdy2);

}

}

}

#pragma acc data copyin(ni, nj, tfac) copy(temp1[0:ni*nj]) \

copyin(temp2[0:ni*nj]) deviceptr(temp)

for (istep=0; istep < nstep; istep++) {</pre>

step_kernel(ni, nj, tfac, temp1, temp2);

// swap the temp pointers

temp = temp1; temp1 = temp2; temp2 = temp;

}

}

```

Figure 3.2: OpenACC implementation of 2D-Heat Equation

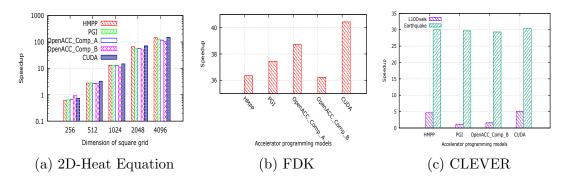

Figure 3.3: Application speedup with different models

once. Without FMA,  $\operatorname{rn}(\operatorname{rn}(X * Y) + Z)$  is composed of two steps and rounded twice. So their results would be slightly different. In 2D-heat equation, this kind of numerical difference will propagate with more iterations. To disable FMA, we used the options "-nvcc-options -fmad=false" in HMPP and "-ta=nofma" in PGI. When we used these compilation flags, the results of both HMPP and PGI are exactly the same as that of the CPU. Figure 3.3 (a) shows performance results when different programming models are applied on this application.

Let us consider the baseline (sequential) speedup to be 1 as shown in the Figure 3.3 (a). We see that for almost all the grid sizes, HMPP and PGI models perform as close as 80% to that of the CUDA version. The CUDA code has been considered from [59]. OpenACC\_Compiler\_A and OpenACC\_Compiler\_B perform approximately 80% and 70% respectively to that of the CUDA version. For the smallest grid size 256\*256 considered, we see that neither the directive-based approaches nor the CUDA version was able to perform better than the sequential version. This is due to the fact that GPU is only suitable for massive computation purposes. For example, we see that for the grid size 4096\*4096, almost all of the directive-based approaches

and CUDA model seem to achieve more than 100% to that of the sequential version.

# 3.2 Feldkamp-Davis-Kress (FDK) Algorithm (Image Processing domain)

Computed Tomography (CT) has been widely used in medical industry to produce tomographic images of specific areas of the body. It uses reconstruction technique that reconstructs an image of the original 3D-object from a large series of two dimensional X-ray images. As a set of rays pass through an object around a single axis of rotation, the produced projection data is captured by an array of detectors, from which a Filtered Back-Projection method based on the Fourier Slice Theorem is typically used to reconstruct the original object. Among various filtered back-projection algorithms, the FDK algorithm [31] is mathematically straightforward and easy to implement. It is important that the acquired reconstruction effect is good, the goal of this work is to speed up the reconstruction using directive-based programming models.

Algorithm 1 shows the pseudo-code of the FDK algorithm, this is comprised of three main steps: Weighting - calculate the projected data; Filtering - filter the weighted projection by multiplying their Fourier transforms; Back-projection - backproject the filtered projection over the 3D-reconstruction mesh. The reconstruction algorithm is computationally intensive and it has biquadratic complexity  $(O(N^4))$ , where N is the number of detector pixels in one dimension. The most time-consuming step of this algorithm is back-projection which takes more than 95% of the whole algorithm. So we will concentrate on parallelizing the back-projection step.

Algorithm 1: Pseudo-code of FDK algorithm

Initialization;

foreach 2D image in detected images do

foreach pixel in image do

Pre-weight and ramp-filter the projection;

end

end

foreach 2D image in detected images do

foreach voxel in 3D reconstruct volume do

Calculate projected coordinate;

Sum the contribution to the object from all tilted fan beams;

end

end

We follow the approach from [44] for implementation purposes. The back-projection has four loops. The three outermost loops will loop over each dimension of the output the 3D object, and the innermost loop will access each of 2D-detected image slices. First the code is restructured so that the three outermost loops are tightly nested and then we can apply collapse clause from PGI and OpenACC and use gridify clause from HMPP. The innermost loop is sequentially executed by every thread. All detected images are transferred from CPU to GPU by using the copyin clause, and the output 3D object (actually many 2D-image slices) are copied from GPU to CPU using the copyout clause. In HMPP, the input/output property of detected images is set as in and output object is set as out. To evaluate our implementations, we use the 3D Shepp-Logan head phantom data which has 300 detected images and the resolution of each image is 200\*200. The algorithm produces 200\*200\*200 reconstructed

cube. Note that this algorithm also has the same issue as 2D-heat conduction i.e. the algorithm is sensitive to floating-point operations, so we disabled the FMA using the compilation flags. This does not mean that the results using FMA are incorrect, but just that we explore different implementation techniques while maintaining the same computation strategy, such that the results are consistent; we will also be able to make a fair comparison of results in this case. Figure 3.3 (b) shows the speedup for different accelerator programming models compared to that of the sequential version. A point to note is that the interval between the points in the Y-axis is small, therefore their performances are actually close to each other. The performance of all directive-based models (HMPP, PGI and OpenACC) are close to 90% of the CUDA code, that was written by us from scratch.

#### 3.3 CLEVER Clustering (Data Mining domain)

In this section, we will parallelize a clustering algorithm called CLEVER (CLustering using representatives and Randomized-hill climbing) [29]. CLEVER is a prototype-based clustering algorithm that seeks for clusters maximizing a plug-in fitness function. Prototype-based clustering algorithms construct clusters by seeking an 'optimal' set of representatives-one for each cluster; clusters are then created by assigning objects in the dataset to the closet cluster representatives. Like K-means [53], it forms clusters by assigning the objects to a cluster with the closest representative. CLEVER uses a randomized-hill climbing to seek a good clustering, i.e. It samples p solutions in the neighborhood of the current solution and continues this

process until no better solutions can be found. Algorithm 2 shows the pseudo-code of CLEVER program code. It starts with randomly selecting k' representatives from the dataset O where k' is provided by the user. CLEVER samples p solutions in the neighborhood of the current solution and chooses the solution s with the maximum fitness value for q(s) as the new current solution provided there is an improvement in the fitness value. New neighboring solutions of the current solution are created by three operators: "Insert" which inserts a new representative into current solution; "Delete" which deletes an existing representative from current solution, and "Replace" which replaces an existing representative with a non-representative. Each operator is selected at a certain probability and the representatives to be manipulated are chosen at random. To prevent premature convergence, CLEVER will resample p\*q more solutions in the neighborhood before terminating, where q is the resampling rate. The description of CLEVER parameters are as follows [24]:

- 1. k': initial number of clusters

- 2. neighborhood-size: maximum numbers of operators applied to generate a solution in the neighborhood

- 3. p: sampling rate, number of samples that is randomly selected from the neighborhood

- 4. q: resampling rate. If the algorithm fails to improve fitness with p and then 2\*p solutions, then sampling size in the neighborhood would be increased by factor q-2

- 5. imax: maximum number of iterations in the algorithm

#### **Algorithm 2:** Pseudo-code of CLEVER algorithm **Input**: Dataset O, k', neighborhood-size, p, q,imax **Output:** Clustering X, fitness q(X), rewards for clusters in X Current solution $\leftarrow$ randomly selecting k' representatives from O; while iterations < imax do Create neighbors of the current solution randomly using the given neighborhood definition, and calculate their respective fitness; if The best neighbor improved fitness then Current solution $\leftarrow$ best neighbor; else Neighborhood of current solution is re-sampled by generating more neighbors; if re-sampling leads to better solution then Current solution $\leftarrow$ best solution found by re-sampling; else Terminate returning the current solution; end end end

We profile the CLEVER algorithm using GNU profiler before parallelizing the same. Statistical information gathered shows that the most time-consuming portion of the algorithm is the function that assigns objects to the closest representative which computes and compares a lot of distances. The original code is written in C++, this needed to be converted to C so that the algorithm could be supported by PGI, HMPP, and OpenACC model. (A point to note is that HMPP recognizes C++ code to an extent).

Since the data structure of the dataset is user-defined and the pointer operation is quite complicated, the accelerator region cannot be parsed by the compiler. Hence, the code is restructured so that it is relatively easier to be parsed by the compiler. The directives also give hints to the compiler such that all the iterations in the loop

are independent. Since the whole dataset is read-only, it is transferred to accelerator before the kernel is called. We can achieve this using both PGI and OpenACC model by using copyin() clause of data construct. We use the region directive of HMPP model and set the data transfer policy of the dataset as atfirstcall so that it is copied from the host to the accelerator only once. This will enable the dataset to stay in the global memory of the accelerator even if the kernel is called many times.

We evaluated the three directive-based models on two datasets called L10Ovals (Large 10Ovals) and Earthquake. The characteristics of these two datasets are shown in Table 3.2 and Table 3.3, respectively. The L10Ovals dataset has natural clusters representing L10Ovals containing 335,900 objects.

Earthquake dataset contains 330,561 earthquakes which are characterized by latitude, longitude, and depth of the earthquake. The goal is to find clusters where the variance of the earthquake depth is high; that is where shallow earthquakes are co-located with deep earthquakes.

Figure 3.3 (c) shows the speedup of how the four different models react to these two datasets. OpenACC\_Compiler\_A required a very long time to execute this algorithm, hence we do not include the speedup in the graph. The reason may be that the model is yet to provide an effective support to deal with pointer operations.

For L10Ovals dataset HMPP showed a speedup of 4.63x, which is very close to that of the CUDA version, 5.04x. We have considered the CUDA version of the algorithm from [24]. We noticed that among the OpenACC models, OpenACC\_Compiler\_B showed a speedup of 1.58x, performing poorer to CUDA. For

Table 3.2: L10Ovals dataset characteristics

| Item                     | Description                       |

|--------------------------|-----------------------------------|

| Data size                | 335,900 objects                   |

| Attributes               | <x, class="" label="" y,=""></x,> |

| Distance Function        | Euclidean Distance                |

| Plug-in Fitness Function | Purity:                           |

|                          | Percentage of objects belonging   |

|                          | to the majority class of          |

|                          | the cluster                       |

Table 3.3: Earthquake dataset characteristics

| Item                     | Description                          |

|--------------------------|--------------------------------------|

| Data size                | 330,561 objects                      |

| Attributes               | < latitude, longitude, depth >       |

| Distance Function        | Euclidean Distance                   |

| Plug-in Fitness Function | High Variance:                       |

|                          | Measures how far the objects in      |

|                          | in the cluster are spread            |

|                          | out with respect to earthquake depth |

Earthquake dataset, the speedup achieved by HMPP, PGI, OpenACC\_Compiler\_B were 29.99x, 29.65x and 29.32x, respectively, these are almost the same as that of CUDA, which showed a speedup of 30.33x. Although L10Ovals and Earthquake have almost the same number of objects in their datasets we still see a significant difference in performance. This is primarily due to the characteristics of each of these datasets. L10Ovals has well defined and separated clusters therefore converges more quickly. The L10Ovals clustering task takes 21 iterations whereas the earthquake dataset clustering takes 216 iterations. Moreover the number of clusters searched in the earthquake clustering experiment is much higher than the number of clusters in L10Ovals experiment making it more time consuming to assign objects to clusters.

Table 3.4 shows the execution time consumed in seconds by the different directive-based models for three case studies. Results for the application 2D-Heat Equation shows that the time consumed by directive-based models were significantly lower than the time consumed by the serial version of the code. However the execution time for the CUDA code still appears to be the best. We see that HMPP model performs better than that of PGI and also that of OpenACC models. It could be due to slightly better optimization strategies offered by HMPP compiler implementations. Among the two OpenACC models, OpenACC\_Compiler\_A seems to perform better than OpenACC\_Compiler\_B. With respect to FDK algorithm, we notice that almost all the models perform similar to each other and in fact close to that of the CUDA code. CLEVER application shows that HMPP model performs the best compared to all other models. As mentioned earlier, we suspect that PGI compiler cannot handle pointer operations very efficiently yet. OpenACC\_Compiler\_A model may also have issues with the implementation of pointer operations. Hence the execution time seems to be long.

To summarize, directive-based models have indeed shown promising results compared to that of the CUDA version. In-depth research analysis of these models would lead to better performance. An important point to note is that the OpenACC model is still being constructed and the technical details may require fine tuning before we could actually make a deeper comparative analysis.

Table 3.4: Time(in sec) consumed by Serial, CUDA, HMPP, PGI and OpenACC versions of the code, only for most time-consuming dataset

| Applications | Serial  | CUDA  | HMPP  | PGI    | OpenACC |       |

|--------------|---------|-------|-------|--------|---------|-------|

|              |         |       |       |        | A       | В     |

| 2D Heat      | 8922.81 | 59.13 | 60.78 | 72.74  | 75.65   | 84.76 |

| FDK          | 363.50  | 8.99  | 10.40 | 9.71   | 9.39    | 10.04 |

| CLEVER       | 116.15  | 23.04 | 25.08 | 101.51 | -       | 73.31 |

#### 3.4 Summary

This chapter evaluates some of the prominent directive-based GPU programming models for three applications with different characteristics. We compare each of these models and tabulate the performances achieved by these models. We see that the performance is highly dependent on the application characteristics. The highlevel models also provide a high-level abstraction by hiding most of the low-level complexities of the GPU platform. This makes programming easier leading to programmer productivity. We noticed that all the directive-based models performed much better than that of the serial versions of the applications being evaluated. We also observed that these models demonstrated performance results close enough to that of the CUDA version of the applications. However, we had to write almost different versions of the code before we could use a particular programming model, especially while using HMPP and PGI. OpenACC solved this portability issue by providing a single standard to be used to program GPUs.

# Chapter 4

# Parallelization and Optimization Strategies using Directive-based Model

In this chapter, we discuss the parallelization strategies to port NAS Parallel Benchmarks (NPB) [18] to GPGPUs using high-level compiler directives, OpenACC. NPB are well recognized for evaluating current and emerging multi-core/many-core hardware architectures, characterizing parallel programming models, and testing compiler implementations. The suite consists of five parallel kernels (IS, EP, CG, MG, and FT) and three simulated computational fluid dynamics (CFD) applications (LU, SP, and BT) derived from important classes of aerophysics applications. Together they mimic the computation and data move- ment characteristics of large scale computational CFD applications [18]. This is one of the standard benchmarks that is close

to real world applications. We believe that the OpenACC programming techniques used in this chapter can be applicable to other models such as OpenMP. Based on the application requirements, we will analyze the applicability of optimization strategies such as array privatization, memory coalescing, and cache optimization [79]. With vigorous experimental analysis, we will then analyze how the performance can be incrementally tuned. To the best of our knowledge, we are the first group to create an OpenACC benchmark suite for the C programs in NPB. Four benchmarks in this suite have been contributed to SPEC benchmark [43].

The performance of NPB benchmarks are well studied for conventional multicore processor based clusters. Results in [42] show that OpenMP achieves good performance for a shared memory multi-processor. Other related works also include NPB implementations of High-Performance Fortran (HPF) [32], Unified Parallel C (UPC) [4] and OpenCL [60]. With high performance computing systems rapidly growing, hybrid-programming models become a natural programming paradigm for developers to exploit hardware characteristics. Wu et al. [72] discussed a hybrid OpenMP + MPI version of SP and BT benchmarks. Pennycook et al. [57] described the MPI+CUDA implementation of LU benchmark. The hybrid implementations commonly yield better performance if communication overhead is significant for MPI implementation and if computation for a single node is well parallelized with OpenMP. NAS-BT multi-zone benchmark was evaluated in [19] using OpenACC and OpenSHMEM hybrid model.

Grewe et al. [34] presented a compiler-based approach that automatically translate OpenMP program to optimized OpenCL code for GPUs and they evaluated all benchmarks in NPB suite. Lee et al. [50] parallelized EP and CG from NPB suite using OpenACC, HMPP, CUDA, and other models and compared the performance differences. But our implementation is different from theirs for these two benchmarks.

#### 4.1 Strategies

One of the main benefits of programming using a directive-based programming model is achieving performance by adding directives incrementally and creating portable modifications to an existing code. We consider the OpenMP version of NPB benchmarks as the starting point. Steps to parallelize legacy code using OpenACC are:

- 1) Profile the application to find the compute intensive parts, which are usually loops.

- 2) Determine whether the compute intensive loops can be executed in parallel. If not, perform necessary code transformations to make the loops parallelizable, if possible.

- 3) Prepend parallel/kernels directives to these loops. The kernels directive indicates that the loop needs to be executed on the accelerator. Using the parallel directive alone will cause the threads to run the annotated code block redundantly, until a loop directive is encountered. The parallel directive is mostly effective for non-loop statements.

- 4) Add data directives for data movement between the host and the device. This directive should be used with care to avoid redundant data movement, e.g. putting

data directives across multiple compute regions. Inside the data region, if the host or device needs some data at the end of one compute region, update host directive could be used to synchronize the corresponding data from the device to host, or update device directive is used if the device needs some data from the host.

- 5) Optimize data structures and array access pattern to efficiently use the device memory. For instance, accessing data in the global memory in a coalesced way, i.e. consecutive threads should access consecutive memory address. This may require some loop optimizations like loop permutation, or transforming the data layout that will change the memory access pattern.

- 6) Apply loop-scheduling tuning. Most of the OpenACC compilers provide some feedback during compilation informing users about how a loop is scheduled. If the user finds the default loop scheduling not optimal, the user should optimize the loop manually by adding more loop directives. This should lead to improvement in speedup.

- 7) Use other advanced optimizations such as the cache directive, which defines the variables to be cached by the kernel. Usage of the async clause will initiate data movement operations and kernel execution as asynchronous activities, thus enabling an overlap with continuous execution by the host CPU.

Some of the above steps need to be applied repeatedly along with profiling and feedback information provided by compiler and profilers. The practices and optimization techniques applied vary depending on the original parallel pattern and code structures of an application. Some of those techniques are summarized in the following sections. While these techniques have been used for optimizing parallel

```

for(k=0; k<N; k++) {

for(j=0; j<N; j++) {

for(i=0; i<N; i++) {

A[j][i] = ...

}

}

}</pre>

```

Figure 4.1: Array privatization example

program on CPUs, applying them on GPUs pose different challenges, particularly when using them in large code bases.

#### 4.1.1 Array Privatization

Array privatization makes different threads access distinct memory addresses, so that different threads do not access the same memory address. It is a technique of taking some data that is common or shared among parallel tasks and duplicating it so that different parallel tasks can have a private copy to operate. Figure 4.1 shows an example for array privatization. If we parallelize the triple-nested loop on the left side of the figure using OpenMP for CPU and only parallelize the outermost loop, each thread handles the inner two loops. The array A could be annotated as OpenMP private clause to each thread, thus no modification is required to keep the memory usage minimal and improve the cache performance. However, this is not the case with OpenACC. In OpenACC, if the compiler still only parallelizes the outermost loop, multiple threads will be reading and writing to the same elements of the array A. This will cause data-race conditions, incorrect results, and potential crashes. An option here is to use the OpenACC private clause which is described in [7]. However, if the number of threads are very large, as typically in GPUs, it is very easy that all copies

of the array exceed the total memory available. Even though sometimes the required memory does not exceed the available device memory, it is possible that the assigned number of threads is larger than the number of loop iterations, and in this case some of the device memory will be wasted since some threads are idle. Also the life time of variable within a private clause is only for a single kernel instance. This limits our choice to apply loop-scheduling techniques since only the outermost loop can be parallelized. If the triple nested loop can be parallelized and each thread executes the innermost statements, thousands of threads still need to be created. Keeping the array A private for each thread will easily cause an overflow of memory available on the accelerator device. The right side of Figure 4.1 shows the array privatized code that addresses this issue. This solution added another dimension to the original array so that all threads can access different memory addresses of the data and no data race will happen.

#### 4.1.2 Loop Scheduling Tuning

When parallelizing loops using OpenACC, parallel/kernels directives are inserted around the loop region. With the parallel directive, the user can explicitly specify how the loop is scheduled by setting whether the loop is scheduled in the level of gang, worker, or vector. With the kernels directive, however, loop scheduling is usually left to the compiler's discretion. Ideally, the compiler performs loop analysis and determines an optimal loop scheduling strategy. Our simple experiments show that, when using the kernels directive, the compiler makes good choices most of the times. But the compiler often opts for the less-efficient loop scheduling when the

```

#pragma acc kernels loop gang

:08

for (k = 0; k <= grid_points[2]-1; k++) {

#pragma acc loop worker

for (j = 0; j <= grid_points[1]-1; j++) {

81:

#pragma acc loop vector

for (i = 0; i <= grid_points[0]-1; i++) {

82:

83:

for (m = 0; m < 5; m++) {

rhs[m][k][j][i] = forcing[m][k][j][i];

84:

85:

86:

}

87:

}

88:

}

```

Figure 4.2: Loop scheduling example

loop level is more than three. Figure 4.2 shows one of the scheduling techniques that delivers efficient loop scheduling. However the default scheduling by some compiler only applies to the loops in lines 82 and 83. The loops in line 80 and 81 are executed sequentially. This default option is very inefficient since the two outer most loops are not parallelized. Work in [65] discusses other loop scheduling mechanisms that could be applied in this context.

#### 4.1.3 Memory Coalescing Optimization